# Addressing Multi-Site Validation via a Modular Hardware Platform

## Garrett Shirley, Yolanda Gonzalez Texas Instruments

#### **Outline**

- Introduction

- Overview of TI's DAC Portfolio

- Validation of DACs

- Single-Site Validation Solution

- Multi-Site Validation Solution

- Motherboard

- Daughter Cards

- Device Cards

- Current State and Conclusion

Addressing Multi-Site Validation via a Modular Hardware Platform

#### Introduction

- Highly-integrated and complex integrated circuits (ICs) increase validation time

- ICs within a product family share basic functionality but may require different test hardware

- Single products exist in multiple packages, requiring more hardware

- ICs require validation at wider temperature range

- Individual validation systems for each product reduce software reuse

- Single site validation systems limit throughput

- A flexible, multi-site system is needed to maintain low product development time

Addressing Multi-Site Validation via a Modular Hardware Platform

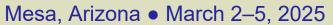

#### Overview of TI's DAC Portfolio

TI's DAC portfolio features wide variety of products with device specific features and functions

AFE881H1

- 16-bit low-power voltage output DAC

- 12-bit ADC, integrated voltage reference and oscillator

- 24 pin QFN package

DAC11001B

- 20-bit unbuffered voltage output DAC

- External buffered voltage reference required

- 48 pin QFP package

DAC530A2W

- 10-bit current and voltage output DACs

- Integrated voltage reference, non-volatile memory

- 16 pin WCSP BGA package

Addressing Multi-Site Validation via a Modular Hardware Platform

#### TestConX 2025

PCB Technology

#### **Validation of DACs**

- DACs require extensive validation due to ATE limitations

- Detailed over-temperature characterization only done by validation engineers, not production ATE

- Some key performance metrics are unable to be fully characterized in production

| DYNAMIC PERFORMANCE          |                                                                                                                             |     |       |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|-------|--|

| Output voltage settling time | 1/4 to 3/4 scale and 3/4 to 1/4 scale settling time to ±2 LSB, AV <sub>DD</sub> = 5.5V, V <sub>REFIN</sub> = 2.5V, gain = 2 | 6   | μs    |  |

| Slew rate                    | AV <sub>DD</sub> = 5.5V, V <sub>REFIN</sub> = 2.5V                                                                          | 1.7 | V/µs  |  |

| Power-on glitch magnitude    | DAC code = zero scale                                                                                                       | 25  | mV    |  |

| Output noise                 | 0.1Hz to 10Hz, DAC code = midscale                                                                                          | 12  | μ∨рр  |  |

| Output noise density         | 1kHz, DAC code = midscale,<br>AV <sub>DD</sub> = 5.5V, V <sub>REFIN</sub> = 2.5V                                            | 65  | nV/Hz |  |

Addressing Multi-Site Validation via a Modular Hardware Platform

#### **Validation of DACs**

- Validation occurs outside of a tester environment

- Engineers aren't constrained by the tester resources

- Requires design of a validation solution capable of testing a given product

- Includes test resource selection, schematic capture, PCB design, software design

- A full validation solution is required to meet all parameters in an acceptable timeframe

Addressing Multi-Site Validation via a Modular Hardware Platform

#### **Validation of DACs**

- All DACs share validation test types

- DAC Linearity: INL, DNL, TUE, Gain Error, Full Scale Error, Offset Error,

Zero Scale Error

- Loading Characteristics: Load Regulation, Output Amplifier Headroom,

Short Circuit Current, Output Impedance

- Dynamic Performance: Output Settling Time, Output Slew Rate, Code Change Glitch Energy, Output Noise, PSRR

- Highly integrated products also share test types

- Internal reference temperature drift

- ADC linearity

- Thermal hysteresis and package stress effects

Addressing Multi-Site Validation via a Modular Hardware Platform

#### **Validation of DACs**

- Specific parameters must be characterized over temperature

- Push for wider -55°C-150°C temperature range in recent years

- Characterization at low temperatures causes icing and condensation, increasing risk of board failure

- Products available in multiple packages require validation of each package type

- Due to shared tests between products there is an opportunity for a generic platform that is adapted to each specific device

Addressing Multi-Site Validation via a Modular Hardware Platform

#### **Single-Site Validation Solution**

- Previous validation solution for DAC team was a single-site platform

- Basic external resources were used to make generic test resources

- Power supplies

- Source/Measure Units

- Analog Inputs/Outputs

- Digital Inputs/Outputs

- Device specific and package specific daughter cards interfaced with motherboard

Addressing Multi-Site Validation via a Modular Hardware Platform

#### TestConX 2025

**PCB** Technology

#### **Single-Site Validation Solution**

- Platform was capable, but had severe limitations

- Excessively complex hardware → Steep learning curve for new engineers

- Static test resources → Unable to adapt to higher voltage/power parts

- Defined for current, not future roadmap devices

- Physically large board → Difficult to fully bring to extreme temperatures

- Many points of failure → Excessive debug time

- Forced-air for temperature characterization → Icing and condensation

- In practice resources only for single site → Limited throughput

- In short: too much, too rigid, too slow

Addressing Multi-Site Validation via a Modular Hardware Platform

<sup>2</sup> 2025

#### **Multi-Site Validation Solution**

- Learning from the single site system, a new system required:

- Modular, flexible hardware

- Generic test resources from external equipment

- Temperature testing done within an temperature chamber (TC)

- Support true multi-site testing for majority of TI DAC devices

- Maintain similar abstraction and separation of responsibilities to deal with different test types and products

Addressing Multi-Site Validation via a Modular Hardware Platform

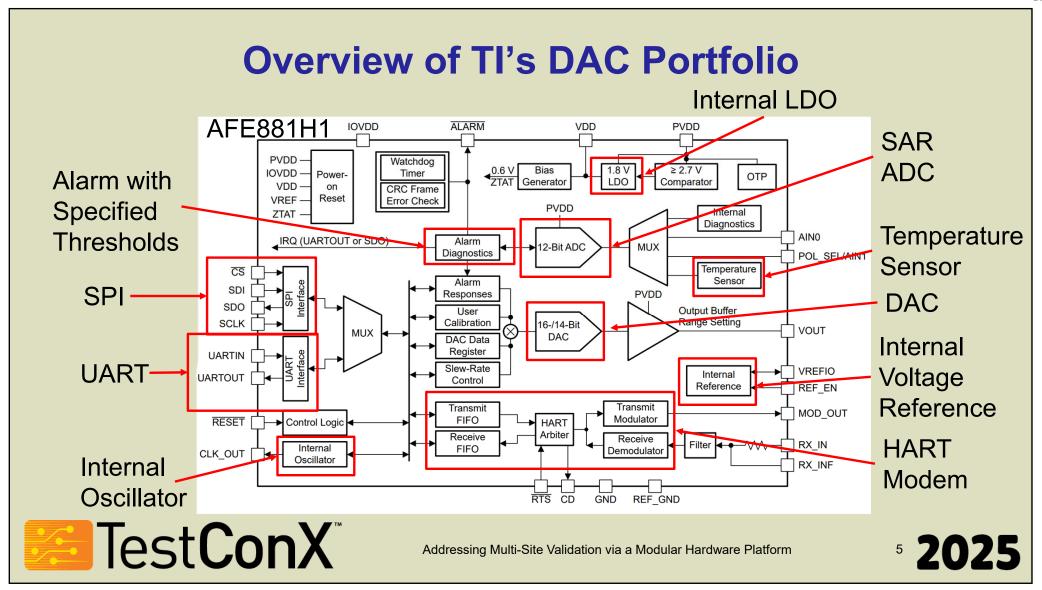

**Daughter Cards**

Motherboard

#### **Multi-Site Validation Solution Architecture**

- 3-Layer hardware stack

- Resource distribution motherboard

- Multiple test specific daughter-cards

- Multiple device specific grand-daughter cards

- Motherboard and daughter-cards externally dock to oven

- Device specific cards contained fully within TC

Addressing Multi-Site Validation via a Modular Hardware Platform

<sup>14</sup> **2025**

Device

Cards

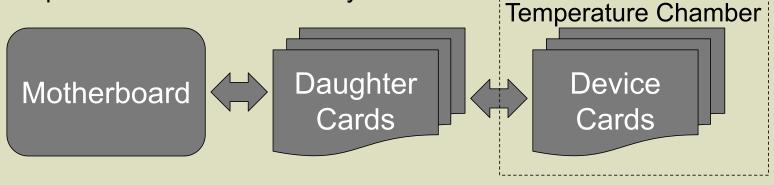

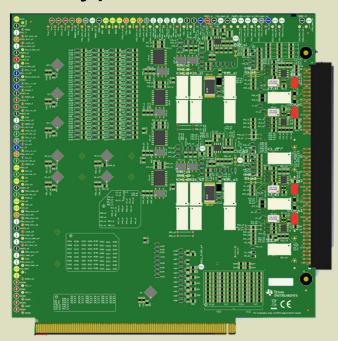

#### **Multi-Site Validation Solution Motherboard**

Single point of interface for all test equipment

Test resources are distributed to multiple daughter cards in 3

ways

Broadcast: Accessible by all daughter cards at all times

- Multiplexed: Accessible by all daughter cards one at a time

- Dedicated: Accessible by a single daughter card at all times

- All test resources come from external equipment

Addressing Multi-Site Validation via a Modular Hardware Platform

<sup>15</sup> **2025**

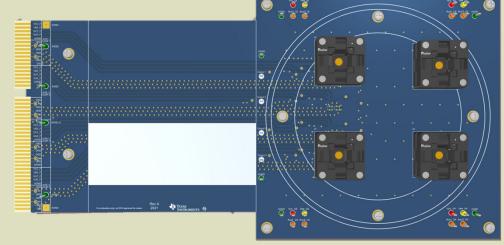

#### Multi-Site Validation Solution Daughter-Cards

- Daughter-cards designed for specific test types

- Voltage output DAC linearity

- ADC linearity

- Voltage reference temperature drift

- Long term drift

- Common pinout/connector to device specific cards

- Highly integrated devices are tested with a combination of daughter-cards

Addressing Multi-Site Validation via a Modular Hardware Platform

<sup>16</sup> **2025**

#### **Multi-Site Validation Solution Device-Cards**

- Only part of the system stressed over temperature

- Only part of the system that is device specific

- Device-cards support multiple DUTs per card

- Different cards for different packages

- Different cards for pre/post solder stress analysis

Addressing Multi-Site Validation via a Modular Hardware Platform

<sup>7</sup> 2025

#### **Systems Compared**

| Parameter                           | Single Site Solution | Multi-Site Solution |

|-------------------------------------|----------------------|---------------------|

| Flexibility                         | Low                  | High                |

| Debug Time                          | High                 | Low                 |

| New Product Development<br>Cost     | Low                  | Low                 |

| Cold Temperature Testing Capability | Low                  | High                |

| Shared Software Across Products     | High                 | High                |

| Multiple Package Testing Capability | High                 | High                |

| Throughput                          | Low                  | High                |

Addressing Multi-Site Validation via a Modular Hardware Platform

#### **Current State and Conclusion**

- First generation motherboard and daughter board in use on pilot project

- Additional daughter boards targeting different parameters in development

- TC based testing allowing -55°C characterization with no icing concerns

- Platform approach and architecture being considered by other TI teams

Addressing Multi-Site Validation via a Modular Hardware Platform

### **Presentation / Copyright Notice**

The presentations in this publication comprise the pre-workshop Proceedings of the 2025 TestConX workshop. They reflect the authors' opinions and are reproduced here as they are planned to be presented at the 2025 TestConX workshop. Updates from this version of the papers may occur in the version that is actually presented at the TestConX workshop. The inclusion of the papers in this publication does not constitute an endorsement by TestConX or the sponsors.

There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

The TestConX logo and 'TestConX' are trademarks of TestConX.