#### TestConX 2025

PCB Technology

## Load Boards: Challenges in Manufacturing for High-Performance Computing

## Tom Bresnan R&D Altanova / Advantest Group

Mesa, Arizona • March 2-5, 2025

TestConX Workshop

www.testconx.org

PCB Technology

#### TestConX 2025

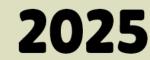

### **For Discussion**

- Market Drivers

- The need for speed

- And more power, too

- Devices getting larger

- Manufacturing Infrastructure

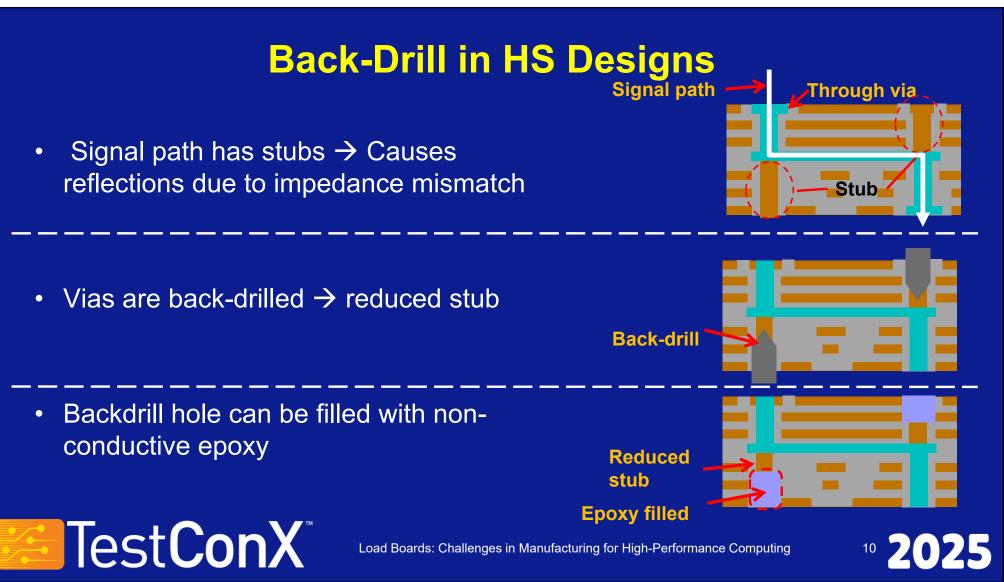

- Back drilling

- Sequential Lamination

- HDI

Load Boards: Challenges in Manufacturing for High-Performance Computing

Session 8 Presentation 1

PCB Technology

TestConX Workshop

www.testconx.org

PCB Technology

#### TestConX 2025

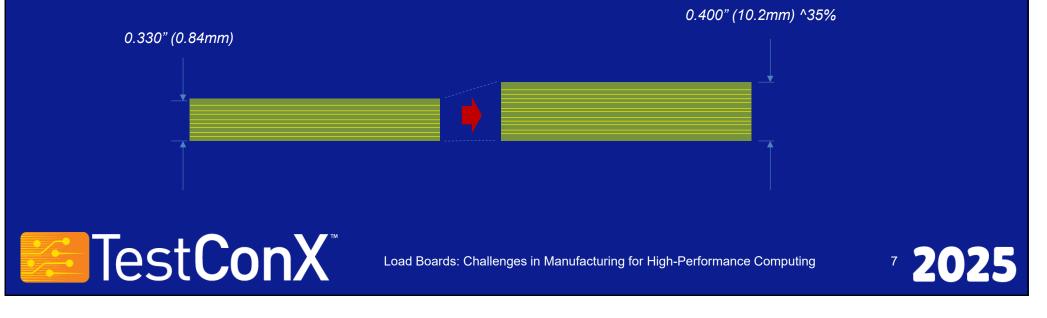

#### **BGA's Are Getting Larger**

- Today = 75mm x 75mm

- Near term roadmaps = 125mm x 125mm

- Long term (<3 years) 150mm x 150mm

Load Boards: Challenges in Manufacturing for High-Performance Computing

#### **TestConX 2025**

PCB Technology **HSIO Challenges Impedance** Control Sintering **Back-Drills Premium Materials** S ш **Drill Accuracy Coaxial Vias** \_\_\_\_ 5 **Material** 0 +/-2 % Impedance Registration 0 **CPO Integrated** Plating Ζ Sockets Т  $\mathbf{O}$ **Feature Control** HDI / Buildup ш 101911 01 (811.) al ⊢ **Materials** 2 – 4 mil Stub Drill Density **Ultra Thick Boards** TestConX<sup>®</sup> <sup>5</sup> 2025

Load Boards: Challenges in Manufacturing for High-Performance Computing

TestConX Workshop

S

ш

5

Ζ

ш

$\triangleleft$

Т

$\mathbf{O}$

www.testconx.org

Session 8 Presentation 1

PCB Technology

TestConX Workshop

www.testconx.org

PCB Technology

#### TestConX 2025

#### **Layer Counts Are Increasing**

- As devices grow, layer counts increase, and panel thickness must also increase

- Layer counts have gone from ~50 layer to >70 and we'll see 100 layers in my lifetime

PCB Technology

#### TestConX 2025

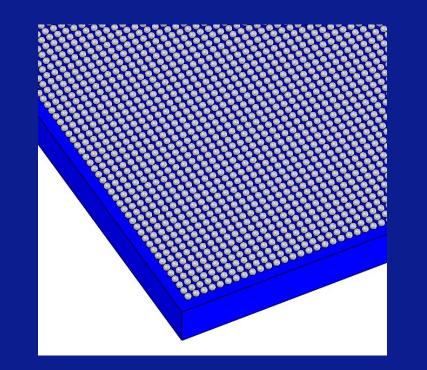

## **PWB Infrastructure**

- Conveyorized equipment

- Developer, Etcher

- Imaging equipment

- Primary and secondary imaging

- Solder mask exposure

- LDI equipment has a limited focal range

Load Boards: Challenges in Manufacturing for High-Performance Computing

PCB Technology

#### TestConX 2025

## **PWB Infrastructure**

- Hole preparation and seed layer deposition

- High(er) aspect ratio plating

- Copper, Nickel, Gold

Load Boards: Challenges in Manufacturing for High-Performance Computing

www.testconx.org

PCB Technology

#### TestConX 2025

## TestConX 2025

PCB Technology

TestConX Workshop

www.testconx.org

PCB Technology

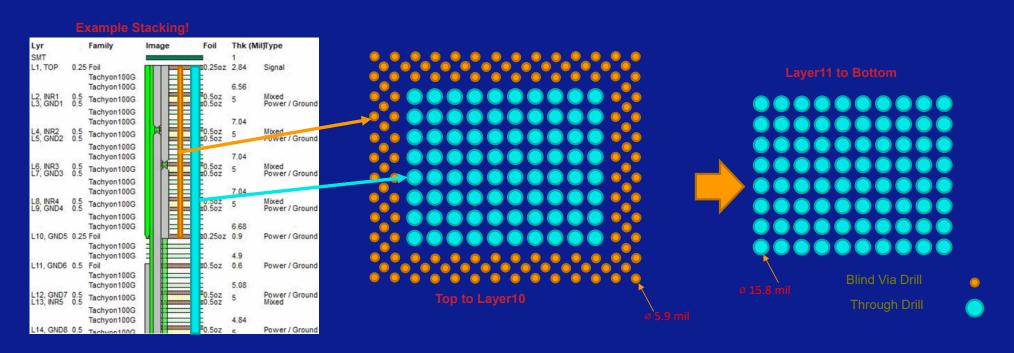

## **An Alternate Strategy – Dual Lamination Stack**

- ✓ Critical Signal of 5.9 or Smaller drills route on Top Book providing Good SI

- ✓ Aspect ratio is greatly improved as finer drills are segregated on upper lamination only!

- ✓ All 2Oz Cu layers on bottom book with GND/PWR via uses bigger drills for better current capacity

- ✓ Upper book can host 0.5Oz power layers of certain critical supplies

- ✓ Improved power delivery to DUT core supplies

Load Boards: Challenges in Manufacturing for High-Performance Computing

PCB Technology

## But Tom, What About HDI?

- Not typically employed in ATE board manufacturing

- Involves advanced techniques and equipment

- Sequential lamination techniques

- adding layers one at a time \$\$ & lead time

Load Boards: Challenges in Manufacturing for High-Performance Computing

PCB Technology

## But Tom, What About HDI?

- HDI employs the use of microvia's, <= 150u diameter

- Material selection is challenging

- those made to withstand the multiple lamination cycles are not the best from a signal performance standpoint

- High-Density Layout

- often involving micro-vias, fine-pitch components, and smaller trace widths.

Load Boards: Challenges in Manufacturing for High-Performance Computing

PCB Technology

## Why not HDI?

- Loopbacks used on ATE boards will require similar number of layers, even with Micro vias and HDI design, not relieving much space around the DUT

- As the HDI will not use pitch transformation, the expected tracewidths/geometry will remain similar, thus not much benefit in layer reduction for high-speed signals

- As described earlier, HDI requires significantly more lead time and cost

Load Boards: Challenges in Manufacturing for High-Performance Computing

PCB Technology

#### TestConX 2025

## **Our discussion today**

- Market drivers

- Device size and the need for speed

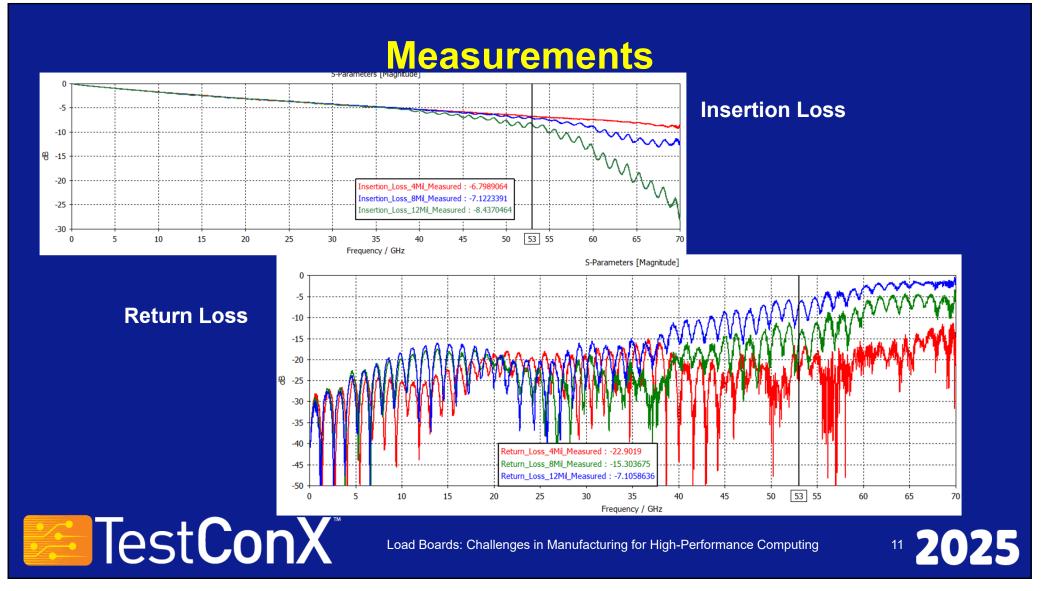

- HSIO challenges & technologies to solve them

- PWB infrastructure

- Alternative PWB constructions

- Thru-hole (w/ back drill), sequential lamination, HDI

Load Boards: Challenges in Manufacturing for High-Performance Computing

# **Presentation / Copyright Notice**

The presentations in this publication comprise the pre-workshop Proceedings of the 2025 TestConX workshop. They reflect the authors' opinions and are reproduced here as they are planned to be presented at the 2025 TestConX workshop. Updates from this version of the papers may occur in the version that is actually presented at the TestConX workshop. The inclusion of the papers in this publication does not constitute an endorsement by TestConX or the sponsors.

There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

The TestConX logo and 'TestConX' are trademarks of TestConX.