Session 5 Presentation 3

Socket Technology

# Enabling Near-DUT Voltage Sense and Control

James Hastings ADVANTEST

Mesa, Arizona • March 2–5, 2025

TestConX Workshop

www.testconx.org

March 2-5, 2025

**ADVANTEST**

Socket Technology

#### TestConX 2025

# Outline

- Key challenges arising from HPC / AI trends and process shrinks

- Status quo, shortcomings of current interconnect solutions

- Interconnect design approach addressing these shortcomings

Enabling Near-DUT Voltage Sense and Control

Socket Technology

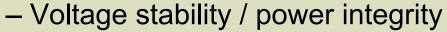

#### **Effects of Power Trend**

- The power / heat dissipation trend combined with fab process shrinks presents 3 key challenges

- Locally concentrated current draw

- Locally concentrated heat dissipation (hot spots)

Related

Socket Technology

Socket Technology

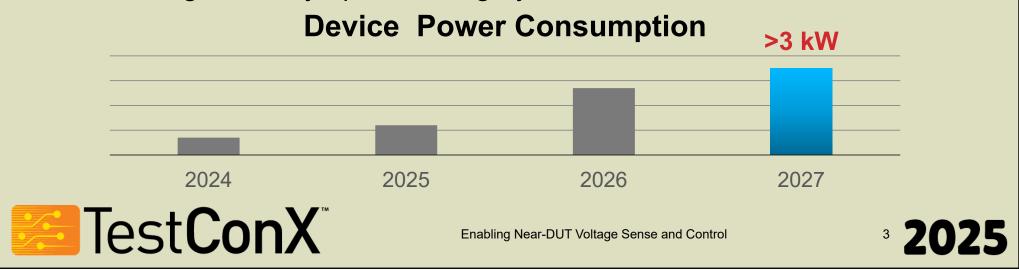

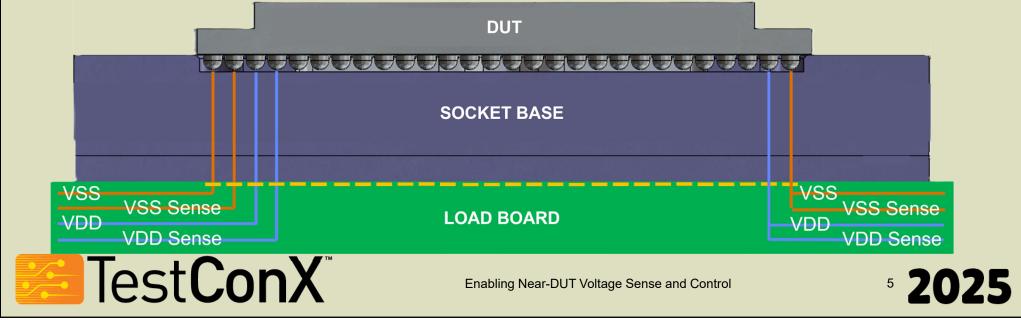

# **Limitations of Standard Interconnects**

- Power integrity becomes more difficult as current and dl/dt increases

- If tester voltage reference is on PCB side of the interconnects, parasitic losses decrease control

- VDD/VSS pins can be repurposed for sensing if there is enough margin

Enabling Near-DUT Voltage Sense and Control

TestConX Workshop

www.testconx.org

March 2-5, 2025

° 2025

Session 5 Presentation 3

#### TestConX 2025

Socket Technology

Socket Technology

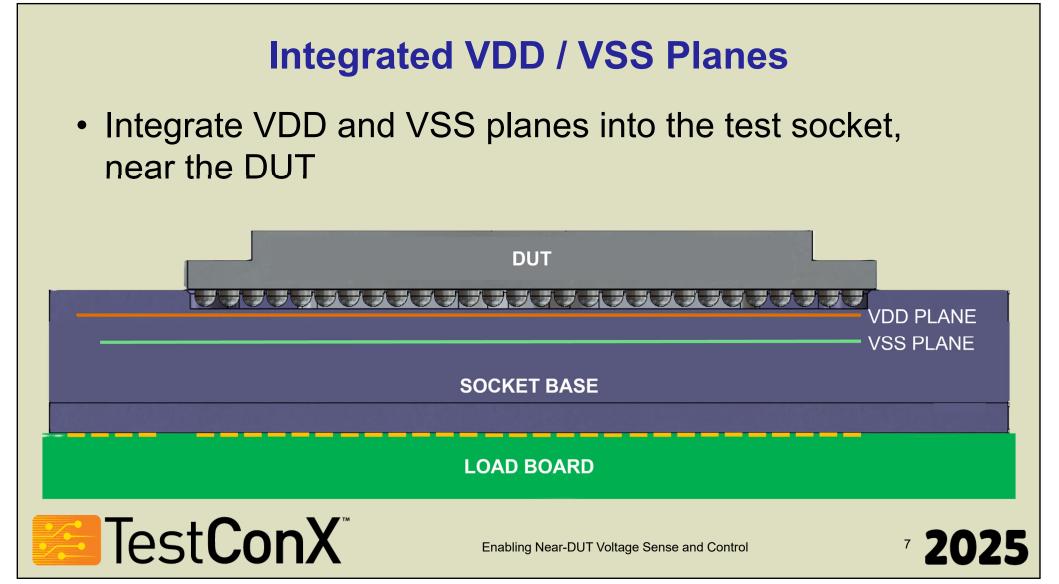

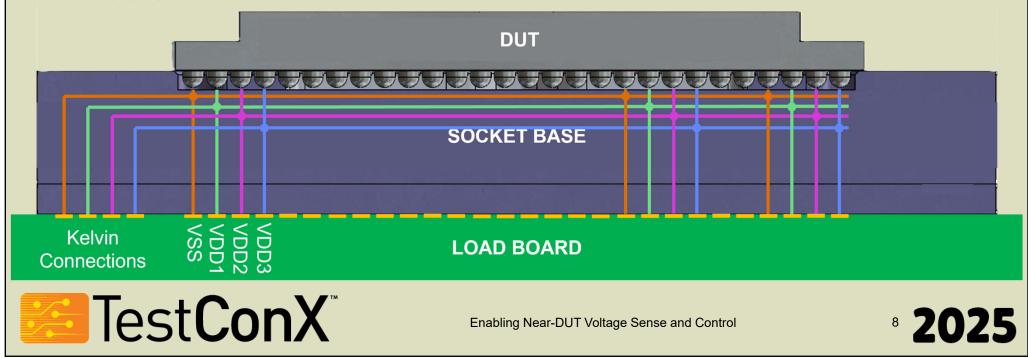

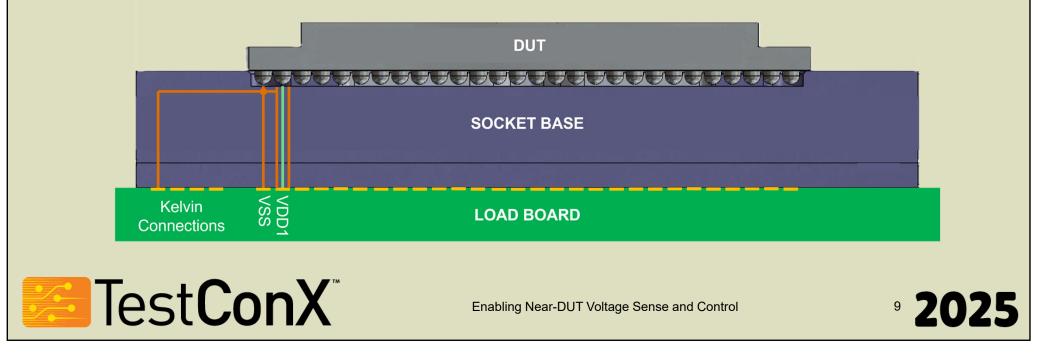

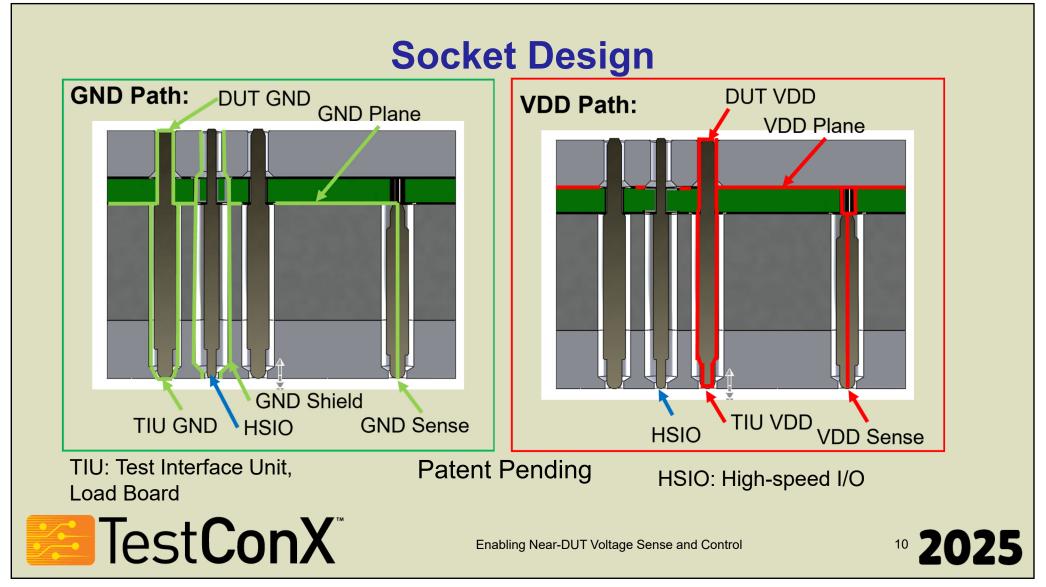

# **Near-DUT Voltage Sensing**

Planes / traces can connect additional VDD/VSS pins outside the DUT footprint for a Kelvin connection to the tester

Socket Technology

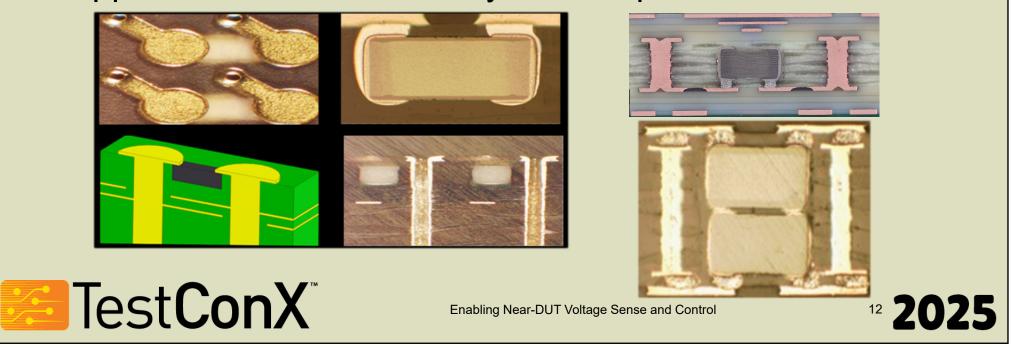

# **Coax Construction**

- Increasing bandwidths / Nyquist requires coax construction to meet NEXT / FEXT requirements

- Impedance tolerance also tightens

Session 5 Presentation 3

#### TestConX 2025

Socket Technology

# **ADDITIONAL CONSIDERATIONS**

Enabling Near-DUT Voltage Sense and Control

TestConX Workshop

www.testconx.org

March 2-5, 2025

Socket Technology

# **Enhanced De-Coupling**

- VDD / VSS planes add capacitance near DUT

- Add capacitors near DUT in some areas / some applications, interstitial may also be possible

Socket Technology

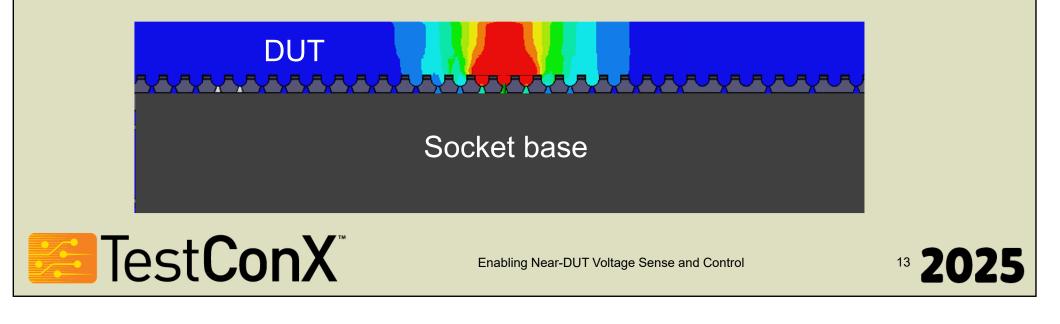

# **Limitations of Standard Interconnects - Thermal**

- Interconnect contact elements (spring probes, etc.) are typically isolated electrically and thermally

- Poor thermal conduction to PCB

- Unable to spread current and heat laterally to mitigate hot spots

Socket Technology

- Electrical current can be spread across the planes

- Socket can act as a heat sink, additional spreading and dissipation

DUT DUT AAAAAA Socket base Socket base VDD/VSS Plane No VDD/VSS Planes Test**ConX**® <sup>14</sup> **2025**

Socket Technology

# **Elastomer Interconnects**

- Why not just use elastomer interconnects?

- Elastomers usually have low inductance and CRES, reducing the parasitic losses

- Not good spreaders or conductors of heat, current can't spread laterally

- Adding de-coupling capacitance difficult

- Voltage measurements / control won't be as accurate

- Without coax, crosstalk can limit bandwidth esp. large pitch devices

Enabling Near-DUT Voltage Sense and Control

Socket Technology

### TestConX 2025

# Summary

- Rapidly increasing power delivery challenges the conventional socket design

- Constructing a socket with integrated planes and circuitry can mitigate several of these challenges

- Voltage sensing at the DUT without sacrificing pins

- Maintain coax shielding along full length of interconnect

- Spreading the current and heat away from localized hot spots

- Embedded capacitance to further mitigate transients

Enabling Near-DUT Voltage Sense and Control

Socket Technology

#### **Acknowledgements**

- "Solving Socket Power Integrity; The Last Link in the Chain", Don Thompson and David Unger, R&D Altanova, TestConX 2022

- "Enabling High-speed Loopback Tests for Serdes, PCIE Gen5/6 on Probe Using Embedded Capacitors on the MLO", Quaid Joher Furniturewala, R&D Altanova, SWTest 2023

Enabling Near-DUT Voltage Sense and Control

# **Presentation / Copyright Notice**

The presentations in this publication comprise the pre-workshop Proceedings of the 2025 TestConX workshop. They reflect the authors' opinions and are reproduced here as they are planned to be presented at the 2025 TestConX workshop. Updates from this version of the papers may occur in the version that is actually presented at the TestConX workshop. The inclusion of the papers in this publication does not constitute an endorsement by TestConX or the sponsors.

There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

The TestConX logo and 'TestConX' are trademarks of TestConX.