Signal Integrity

# Challenges and Strategies for Testing 224 Gbps SerDes

#### Don Thompson PTSL

Mesa, Arizona • March 2–5, 2025

TestConX Workshop

www.testconx.org

March 2-5, 2025

Signal Integrity

#### Why Do We Need 224 Gbps?

- AI: Faster data processing for complex model training

- The speed of the link between nodes is the primary limiter of the AI network

- Internet: Smoother streaming, quicker downloads, lower latency

- HPC: Accelerated scientific research and simulations

- Data Centers: Improved performance and efficiency

- Telecom (5G/6G): Supports next-gen mobile networks and applications

- Autonomous Vehicles: Real-time data processing for safe autonomous navigation

- Industrial Automation: Enhanced efficiency and control

Challenges and Strategies for Testing 224 Gbps SerDes

Test**ConX**

#### TestConX 2025

Signal Integrity

Challenges and Strategies for Testing 224 Gbps SerDes

www.testconx.org

March 2-5, 2025

Signal Integrity

Signal Integrity

#### Migrating from 112 Gbps to 224 Gbps

Initially, these were our concerns, in order of perceived risk:

- 1. Through hole vias

- 2. Trace length

- 3. Sockets

- 4. Loopback components

- 5. Manufacturing tolerances

Challenges and Strategies for Testing 224 Gbps SerDes

Signal Integrity

#### TestConX 2025

## **Through-Hole Vias**

- Vias MUST be optimized using a 3D field solver (e.g. HFSS or CST)

- The via impedance must be matched with the target impedance (Note: SerDes is often 85 Ω or 92 Ω)

- Impedance is tuned by adjusting the drill diameter and copper plane keep-outs to adjust the capacitance and inductance

- Performance for a good tuned impedance via is historically around 45 to 50 GHz

TestConX Workshop

Challenges and Strategies for Testing 224 Gbps SerDes

Signal Integrity

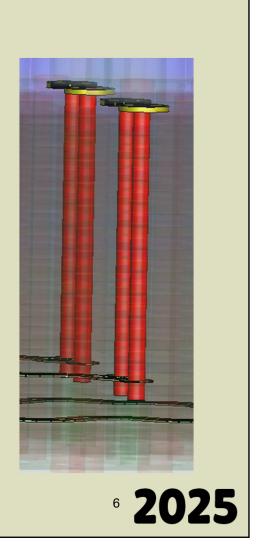

### **Trace Loss: A Problem of Physics, Part 1**

- As frequency increases, loss increases exponentially thus a mostly straight line on a dB plot

- Skin depth has a square root relationship with  $R_{skin}(f) \propto \sqrt{f}$  frequency

- Dielectric loss is linear with frequency

- In our area of interest (5GHz to 56 GHz) trace loss is mostly linear on a dB vs frequency plot

Challenges and Strategies for Testing 224 Gbps SerDes

www.testconx.org

$\mathsf{P}_{\mathsf{loss}}(f) \propto f$

2025

Signal Integrity

#### **Trace Loss: A Problem of Physics, Part 2**

- Trace loss is primarily a function of conductor loss and dielectric loss

- Conductor loss is dominated by "skin effect"

- Dielectric loss is defined by the material's loss tangent

- Trace loss is additive per unit length (3dB + 3dB = 6dB)

- 224 Gbps PAM4 is 1.5x to 2x more lossy versus 112 Gbps PAM4

- <u>This means more loss for</u> <u>same trace length!</u>

#### TestConX 2025

Signal Integrity

#### The Conclusion Is.... Traces must get shorter or Traces must get wider Physics Sux! or Dielectrics must get better or Copper must get smoother or more likely the silicon must accept more loss! Picture by M. Irkham Saddad Test**ConX** <sup>9</sup> 2025 Challenges and Strategies for Testing 224 Gbps SerDes

Difficulty

<sup>10</sup> 2025

#### TestConX 2025

Signal Integrity

#### **Typical 224 Gbps Test Options**

#### SerDes Test Options

- Direct loopback Two vias, trace

- DUT to connector Two vias, trace, connector launch

- Capacitor Four vias, trace, capacitor pads, capacitor

- Four vias, trace, switch pads, switch

- Bias tee

Four vias, trace, inductor and capacitor pads, capacitor, 2x inductors

– Switch

Challenges and Strategies for Testing 224 Gbps SerDes

www.testconx.org

March 2-5, 2025

Signal Integrity

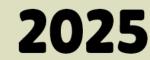

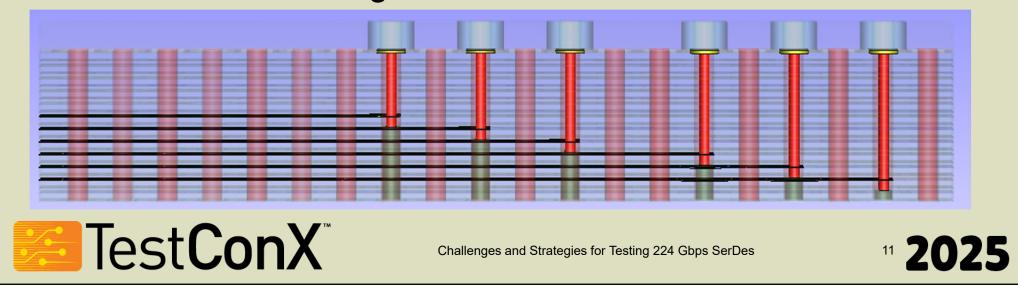

#### Let's start with a 112 Gbps Load Board

- Six routing layers in a single lamination design

- Uses impedance controlled vias with back-drilling

- Loopback through a bias tee

- 85  $\Omega$  differential signals

Signal Integrity

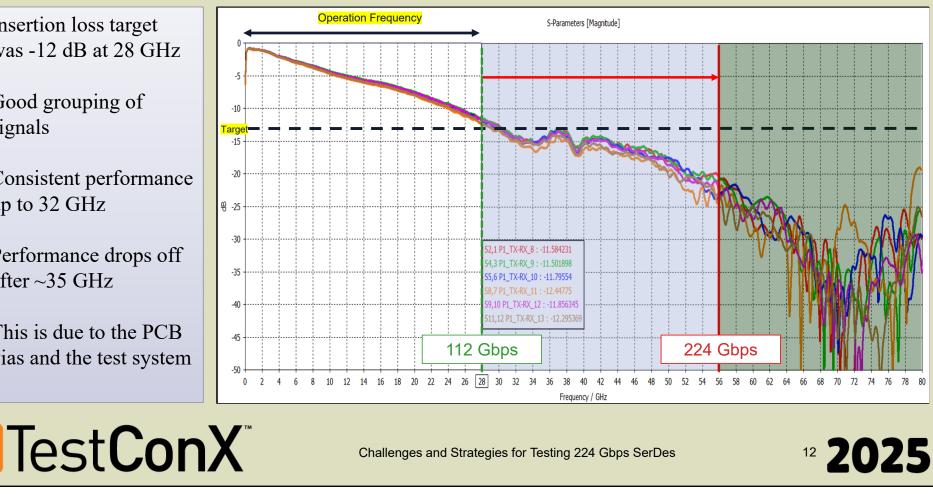

#### **112 Gbps PCB Measured Insertion Loss**

- Insertion loss target was -12 dB at 28 GHz

- Good grouping of ٠ signals

- Consistent performance up to 32 GHz

- Performance drops off ٠ after ~35 GHz

- This is due to the PCB vias and the test system

#### TestConX 2025

Signal Integrity

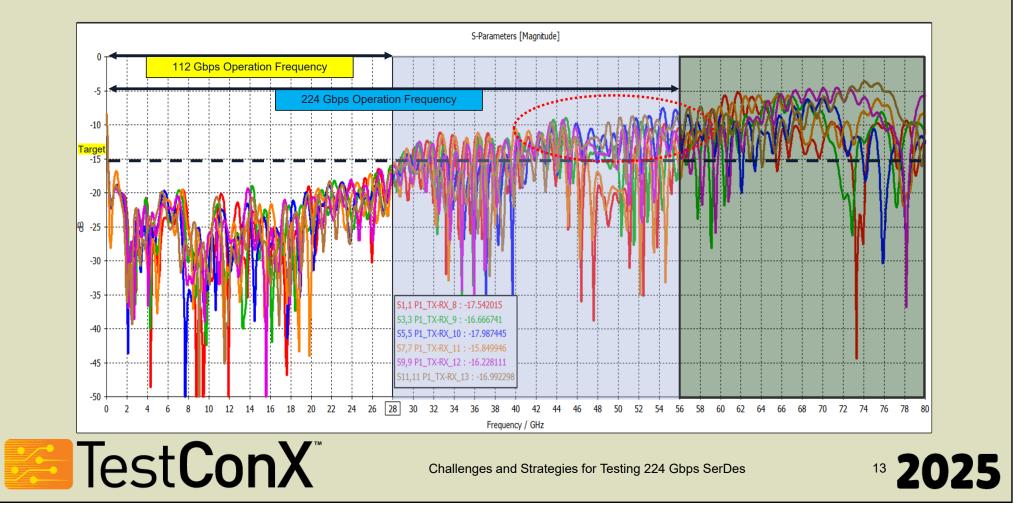

#### **112 Gbps PCB Measured Return Loss**

Signal Integrity

#### **TestConX 2025**

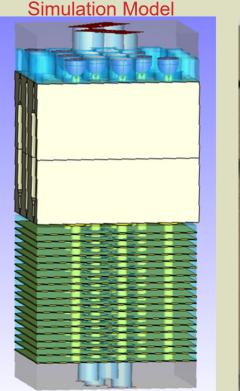

#### 224 Gbps Socket

- Strongly recommend coax or elastomer sockets. This gives us:

- Consistent bandwidth

- Multiple impedance options (e.g. 100  $\Omega$ and 85  $\Omega$  in one design)

- Reduced crosstalk

- Socket simulation needs to be integrated with the load board

- Strongly recommend that a single • party is responsible for both the socket and the load board

Socket -oad Board

2 0

Challenges and Strategies for Testing 224 Gbps SerDes

Signal Integrity

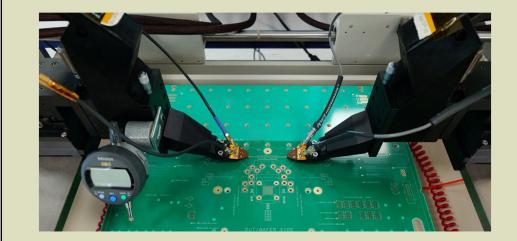

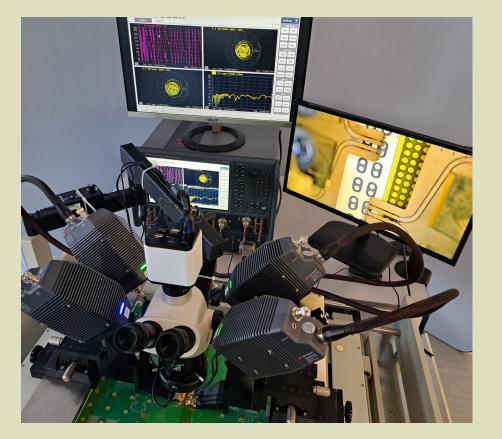

### 224 Gbps Evaluation PCB: Test Setup

#### **Test Configuration**

- 4 Port VNA

- IFBW = 3kHz

- 1mm cable to NuvoRF probe

- 4 Port @ 70 GHz

- Calibration to the end of the 1.0 mm cable

Test**ConX**®

Challenges and Strategies for Testing 224 Gbps SerDes

Signal Integrity

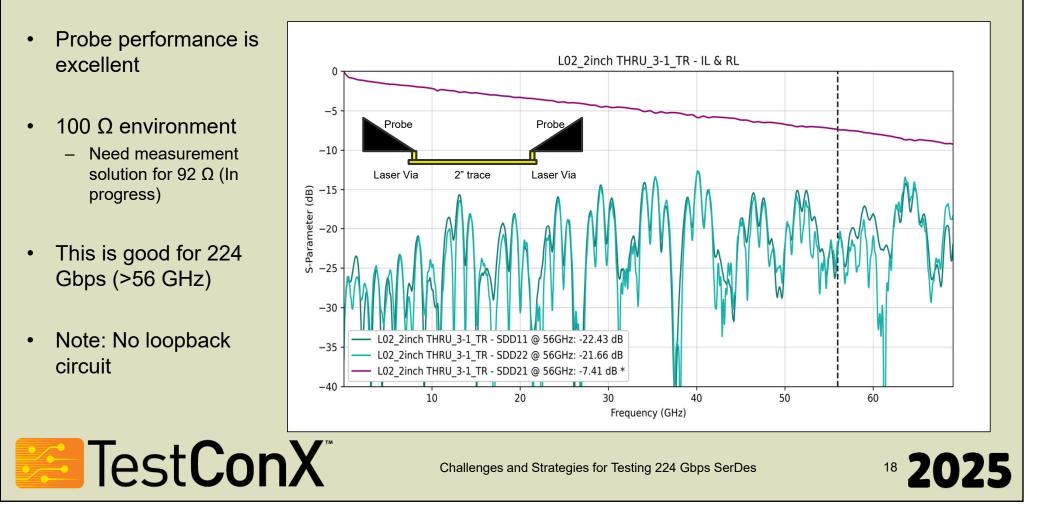

#### 224 Gbps Measurement Challenges

- We didn't find a 70 GHz differential probe available in the market – so we made our own

- Hard to get accurate measurements when measuring 85  $\Omega$  or 92  $\Omega$  differential with a 100  $\Omega$  measurement system

- Gating, calibration, or de-embedding pose problems for 100  $\Omega$  to 85  $\Omega$  measurement environments

- Need a custom probe to solve this challenge

- Need 85  $\Omega$  or 92  $\Omega$  calibration substrates to match the circuit impedance

Challenges and Strategies for Testing 224 Gbps SerDes

Test**ConX**

Signal Integrity

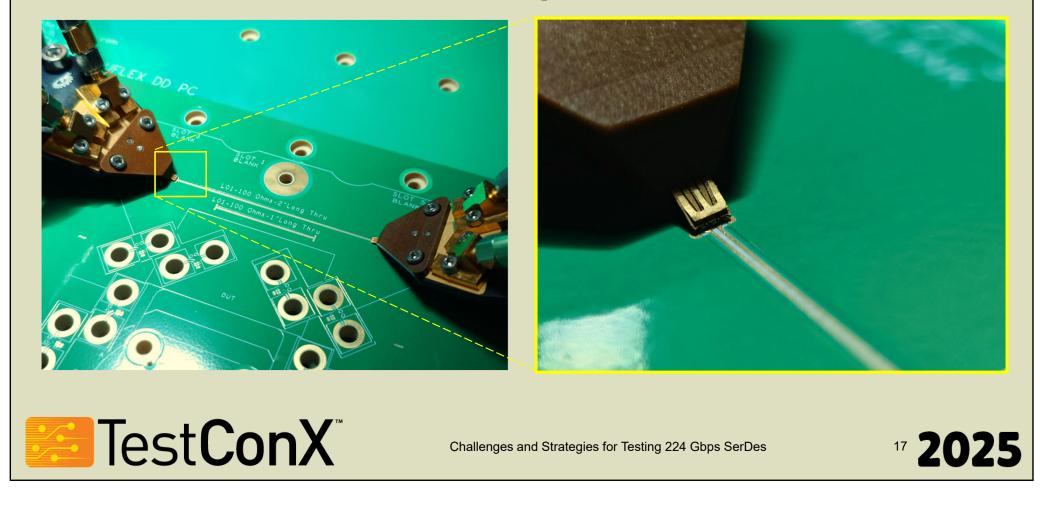

### 224 Gbps Evaluation PCB: PTSL NuvoRF 224 Gbps GSSG 500 Probe

TestConX Workshop

www.testconx.org

March 2-5, 2025

#### TestConX 2025

Signal Integrity

#### 224 Gbps Evaluation PCB: Laser Vias

Signal Integrity

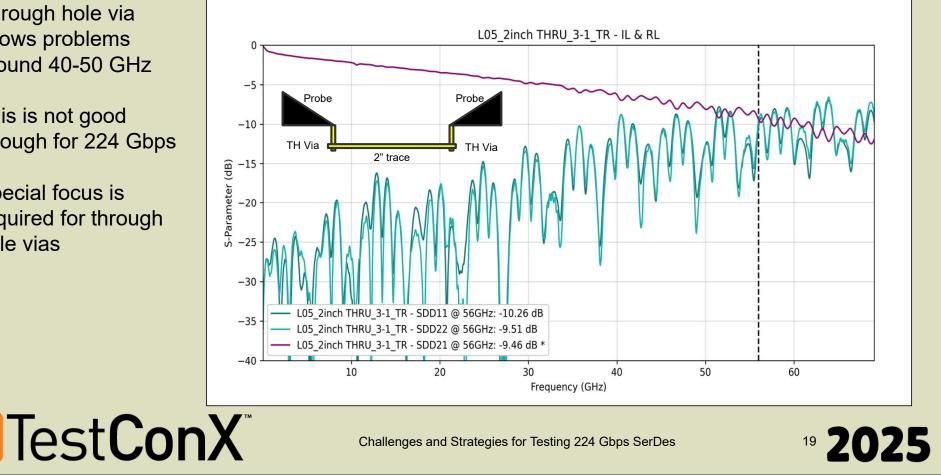

#### **224 Gbps Evaluation PCB: Through Hole Vias**

- Through hole via ٠ shows problems around 40-50 GHz

- This is not good ٠ enough for 224 Gbps

- Special focus is ٠ required for through hole vias

Signal Integrity

#### TestConX 2025

#### Conclusions

- Standard via tuning is not good enough. A special via structure is needed to get to 56 GHz / 224 Gbps PAM4

- The best loopback strategy has yet to be identified

- Measuring this is difficult

- 85  $\Omega$  or 92  $\Omega$  requires special tools and techniques

- 56 GHz large pitch differential is especially challenging

Challenges and Strategies for Testing 224 Gbps SerDes

#### TestConX 2025

Signal Integrity

#### **Special Thanks**

- Robin Cedeno

- Ross McMillan

- Tim Rey

Challenges and Strategies for Testing 224 Gbps SerDes

# **Presentation / Copyright Notice**

The presentations in this publication comprise the pre-workshop Proceedings of the 2025 TestConX workshop. They reflect the authors' opinions and are reproduced here as they are planned to be presented at the 2025 TestConX workshop. Updates from this version of the papers may occur in the version that is actually presented at the TestConX workshop. The inclusion of the papers in this publication does not constitute an endorsement by TestConX or the sponsors.

There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

The TestConX logo and 'TestConX' are trademarks of TestConX.