#### TestConX 2025

Signal Integrity

**Signal Integrity and Power Integrity Test Hardware Design Requirements, Challenges for low** voltages high performance SOC Noel Del Rio, Sean Young, Matt Lauderdale **NXP Semiconductor - Austin** Test**ConX** Mesa, Arizona • March 2–5, 2025

#### TestConX 2025

Signal Integrity

#### Contents

- Power Integrity Challenges of low voltage devices for multi-site Test load boards.

- Signal Integrity Impact of small pitch packages high performance SOC.

- Multi-IP provider on a single SOC.

- Noise floor management and sensitivity for Digital and Mixed-Signal devices.

- Recommendation, Conclusion.

Signal Integrity and Power Integrity Test Hardware Design Requirements, Challenges for low voltages high performance SOC

Signal Integrity

#### **Critical details for low voltage SOC**

- Supply voltage levels trending down to 0.76V, 0.60V....

- The 5.00 % of 0.76 V is 38.00 mV.

- The 5.00 % drop of 15.00 A supply is 2.50 mΩ. Single digit impedance for major IPs such as VDD-Core, DDR, Analog Block.

Signal Integrity and Power Integrity Test Hardware Design Requirements, Challenges for low voltages high performance SOC

Signal Integrity

#### **Power delivery for low voltage SOC**

- Power plane design, layout and geometries.

- Power plane design for multi-site load board.

- Power filter design, components, and placements.

- Power Connector specifications and precisions in time domain and frequency domain.

Signal Integrity and Power Integrity Test Hardware Design Requirements, Challenges for low voltages high performance SOC

Signal Integrity

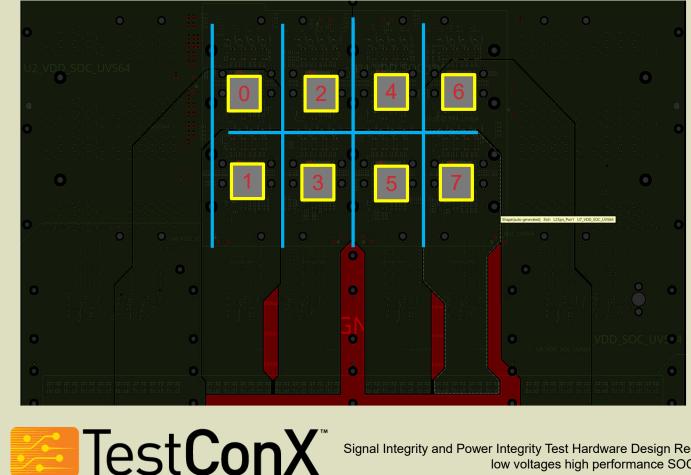

#### **Power Integrity challenges for low voltage SOC**

Test Issues related to power distribution

- Site to site correlation on high current, high performance IPs (e.g., di/dt for Core, DDR, Analog Block).

- IP signal a noise to another IP.

- Cross-talk: Site signal a noise to another site.

Signal Integrity and Power Integrity Test Hardware Design Requirements, Challenges for low voltages high performance SOC

Signal Integrity

6

# PCB Design Solutions for low voltage SOC

Signal Integrity and Power Integrity Test Hardware Design Requirements, Challenges for low voltages high performance SOC

TestConX Workshop

www.testconx.org

March 2-5, 2025

#### TestConX 2025

Signal Integrity

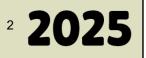

- **Critical Geometries** to ensure correlation between sites.

- **ATE Symmetric** ۰ instruments layout per associated sites.

- The entire power plane is used for a single DUT power, VDD.

- Additional layers for power distribution.

Signal Integrity and Power Integrity Test Hardware Design Requirements, Challenges for low voltages high performance SOC

Signal Integrity

#### Additional power layers for low voltage SOC

|   | L5/pn_Gnd28 |       |      |      |      |     |   |  |

|---|-------------|-------|------|------|------|-----|---|--|

|   | L58pn_Pwr10 |       |      |      |      |     |   |  |

|   | L59pn_Gnd29 |       |      |      |      |     |   |  |

|   | L60pn_Pwr11 |       |      |      |      |     |   |  |

|   | L61pn_Gnd30 |       |      |      |      |     |   |  |

|   | L62pn_Pwr12 |       |      |      |      |     |   |  |

|   | L63pn_Gnd31 |       |      |      |      |     |   |  |

|   | L64pn_Pwr13 |       |      |      |      |     |   |  |

|   | L65pn_Gnd32 |       |      |      |      |     |   |  |

|   | L66sp_Inr20 |       |      |      |      |     |   |  |

|   | L67pn_Gnd33 |       |      |      |      |     |   |  |

|   | L68sp_Inr21 |       |      |      |      |     |   |  |

|   | L69pn_Gnd34 |       |      |      |      |     |   |  |

|   | L70sp_Inr22 |       |      |      |      |     |   |  |

| × | L71pn_Gnd35 |       |      |      |      |     |   |  |

| ^ | L72sp_Inr23 |       |      |      |      |     |   |  |

|   | L73pn_Gnd36 |       |      |      |      |     |   |  |

|   | L74sp_Inr24 |       |      |      |      |     |   |  |

|   | L75pn_Gnd37 |       |      |      |      |     |   |  |

|   | L76sp_Inr25 |       |      |      |      |     |   |  |

|   | L77pn_Gnd38 |       |      |      |      |     |   |  |

|   | L78sp_Inr26 |       |      |      |      |     |   |  |

|   | L79pn_Gnd39 |       |      |      |      |     |   |  |

|   | Bottom      |       |      |      |      |     |   |  |

|   | Through All |       |      |      |      |     |   |  |

|   |             | nable | Inte |      | loct |     |   |  |

|   |             | mable | Taye | n se | iect | mod | e |  |

|             | <br> | <br> | <br>         |

|-------------|------|------|--------------|

| L22pn_Gnd11 |      |      |              |

| L23pn_Pwr1  |      |      | $\checkmark$ |

| L24pn_Gnd12 |      |      |              |

| L25pn_Pwr2  |      |      |              |

| L26pn_Gnd13 |      |      |              |

| L27pn_Pwr3  |      |      |              |

| L28pn_Gnd14 |      |      |              |

| L29pn_Pwr4  |      |      |              |

| L30pn_Gnd15 |      |      |              |

| L31pn_Pwr5  |      |      |              |

| L32pn_Gnd16 |      |      |              |

| L33pn_Pwr6  |      |      |              |

| L34pn_Gnd17 |      |      |              |

| L35sp_Inr11 |      |      |              |

| 136nn Gnd18 |      |      |              |

| L53pn_Gnd26 |  |  |  |  |

|-------------|--|--|--|--|

| L54pn_Pwr8  |  |  |  |  |

| L55pn_Gnd27 |  |  |  |  |

| L56pn_Pwr9  |  |  |  |  |

| L57pn_Gnd28 |  |  |  |  |

| L58pn_Pwr10 |  |  |  |  |

| L59pn_Gnd29 |  |  |  |  |

| L60pn_Pwr11 |  |  |  |  |

| L61pn_Gnd30 |  |  |  |  |

| L62pn_Pwr12 |  |  |  |  |

| L63pn_Gnd31 |  |  |  |  |

| L64pn_Pwr13 |  |  |  |  |

| L65pn_Gnd32 |  |  |  |  |

|             |  |  |  |  |

|             |  |  |  |  |

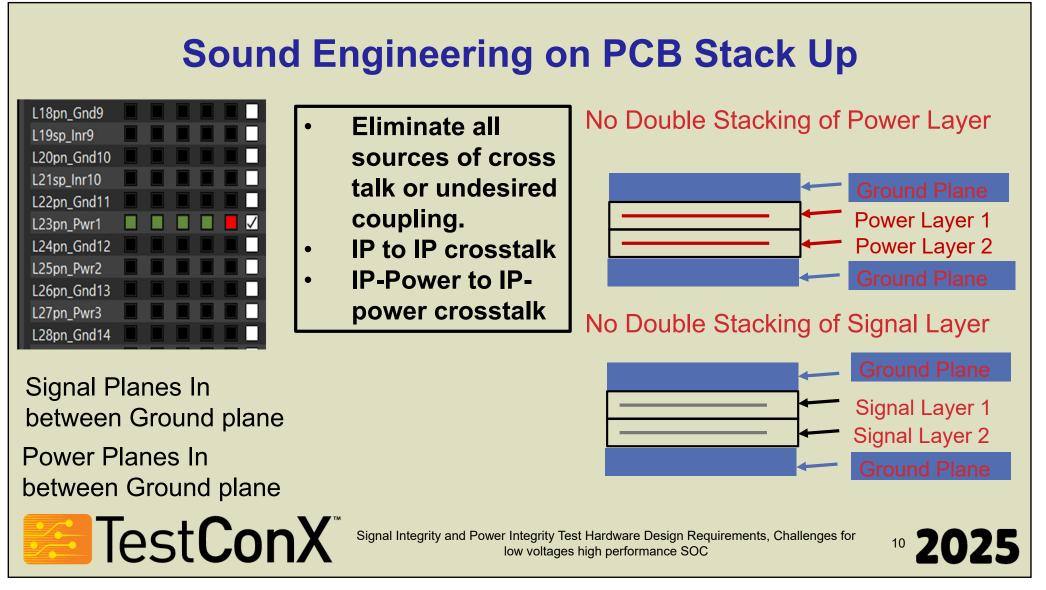

The need for more power plane layers

- Power delivery requires precise power plane design.

- Additional layer count is inevitable.

- Electrical, mechanical complexities associated with thick boards.

80+ layer PCB

Test**ConX**

Signal Integrity and Power Integrity Test Hardware Design Requirements, Challenges for low voltages high performance SOC

٠

Session 3 Presentation 1

Signal Integrity

#### TestConX 2025

Signal Integrity

Signal Integrity

11

## Signal Integrity Sensitivity on small pitch and low voltage SOC

Signal Integrity and Power Integrity Test Hardware Design Requirements, Challenges for low voltages high performance SOC

TestConX Workshop

www.testconx.org

March 2-5, 2025

Signal Integrity

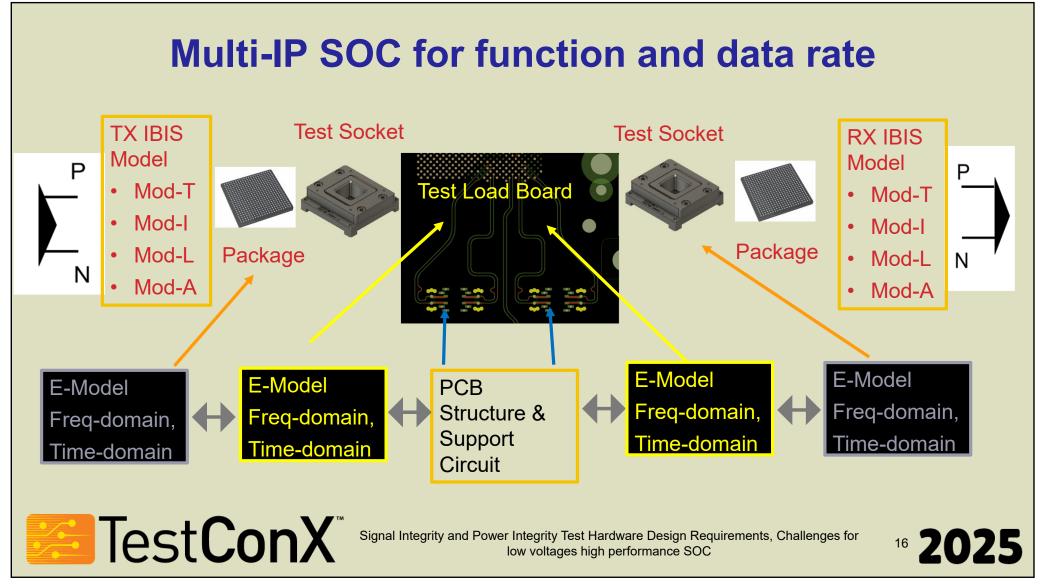

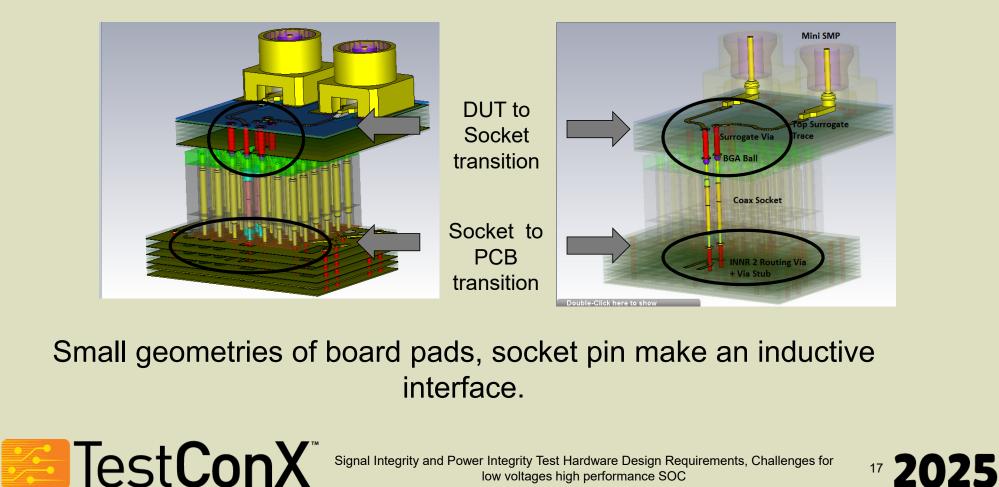

# Intricacies of Small Pitch Packages, Multi-Ip Iow voltage high performance SOC

- Inductive physical circuits on transmission line segment interface is common. Focus on hardware integration is a must to avoid SI issue as a function of frequency.

- Small board pads.

- Small diameter socket pins.

- Physical 3D modeling of hardware integration is very critical.

- Board Geometries, Structures, over all thickness is predicated by package pitch.

Signal Integrity and Power Integrity Test Hardware Design Requirements, Challenges for low voltages high performance SOC

Signal Integrity

# Intricacies of Small Pitch Packages, Multi-Ip Iow voltage high performance SOC

- IP specific Impedance (e.g. Differential Impedance-> PCIE=85 Ω, DDR=80 Ω, USB=90 Ω, STD I/O 100 Ω).

- Standard Single Impedance Socket.

- Coaxial Single Impedance Socket.

- Coaxial Multi-Impedance Socket.

- Type of Pin, & Pin-Tip Design.

- DUT Grid surface design, structure becomes complicated as a function of socket technology.

Signal Integrity and Power Integrity Test Hardware Design Requirements, Challenges for low voltages high performance SOC

Signal Integrity

### Multi-IP on small pitch and low voltage SOC

Signal Integrity and Power Integrity Test Hardware Design Requirements, Challenges for low voltages high performance SOC

14

#### TestConX 2025

Signal Integrity

|                                                                                                                                                   |       | IP specific l                        | npedai             | nce                                                   |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------|--------------------|-------------------------------------------------------|--|

| IP Type                                                                                                                                           | Model | Impedance (Diff)<br>(Specifications) | Data<br>Rate       | Modeled, Simulated<br>best results<br>Impedance range |  |

| PCIE                                                                                                                                              | Т     | 85 Ω                                 | 16 Gbps            | 85 $\Omega$ to 90 $\Omega$                            |  |

| DDR                                                                                                                                               | Т     | 80 Ω(40 Ω SE)                        | 8 Gbps             | 90 $\Omega$ to 100 $\Omega$                           |  |

| Ethernet                                                                                                                                          | I/A   | 85 Ω 100 Ω                           | 16 Gbps            | 85 $\Omega$ to 90 $\Omega$                            |  |

| PCIE                                                                                                                                              | I/A   | 85 Ω                                 | 10,16,<br>2.5 Gbps | 85 $\Omega$ to 90 $\Omega$                            |  |

| USB3                                                                                                                                              | Ι     | 90 Ω                                 | 10 Gbps            | 90 Ω                                                  |  |

| DDR                                                                                                                                               | I/T/A | 80 Ω (40 Ω SE)                       | 4 Gbps             | 90 $\Omega$ to 100 $\Omega$                           |  |

| PCIE                                                                                                                                              | L/A   | 100 Ω 85 Ω                           | 28,32,45<br>Gbps   | 85 $\Omega$ to 100 $\Omega$                           |  |

| TestConX <sup>™</sup> Signal Integrity and Power Integrity Test Hardware Design Requirements, Challenges for low voltages high performance SOC 15 |       |                                      |                    |                                                       |  |

Session 3 Presentation 1

Signal Integrity

Signal Integrity

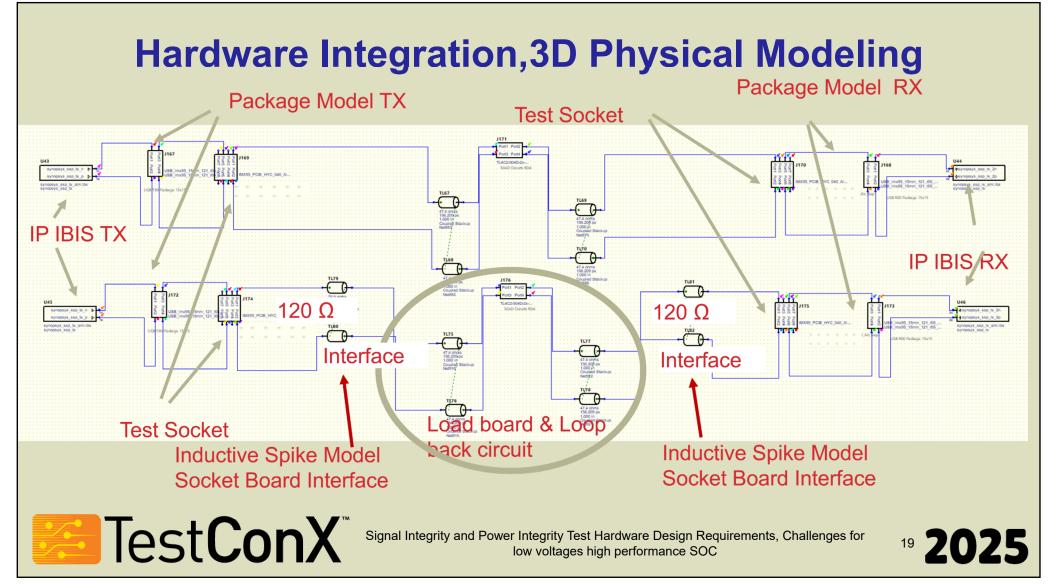

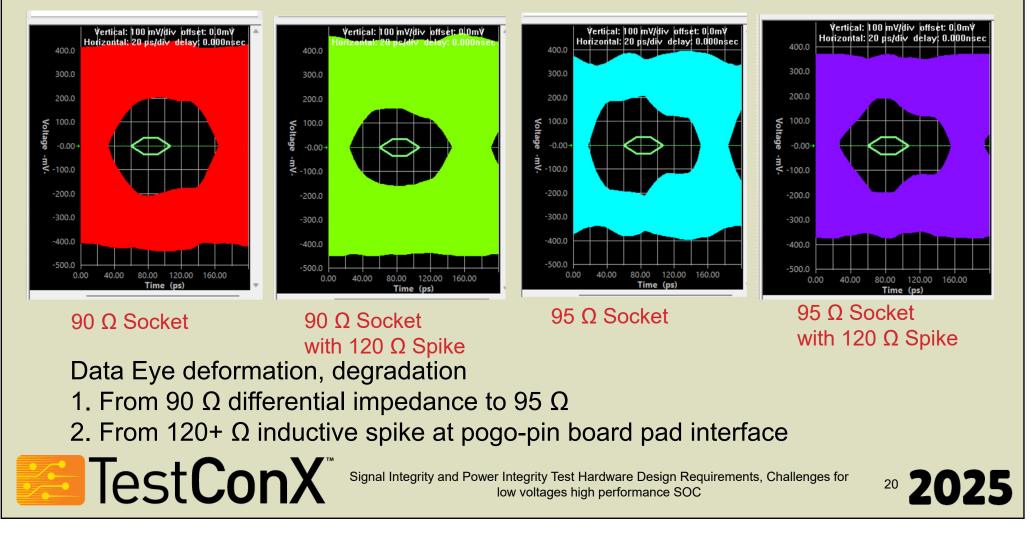

#### Hardware Integration, 3D Physical Modeling

Signal Integrity

#### Hardware Integration, 3D Physical Modeling

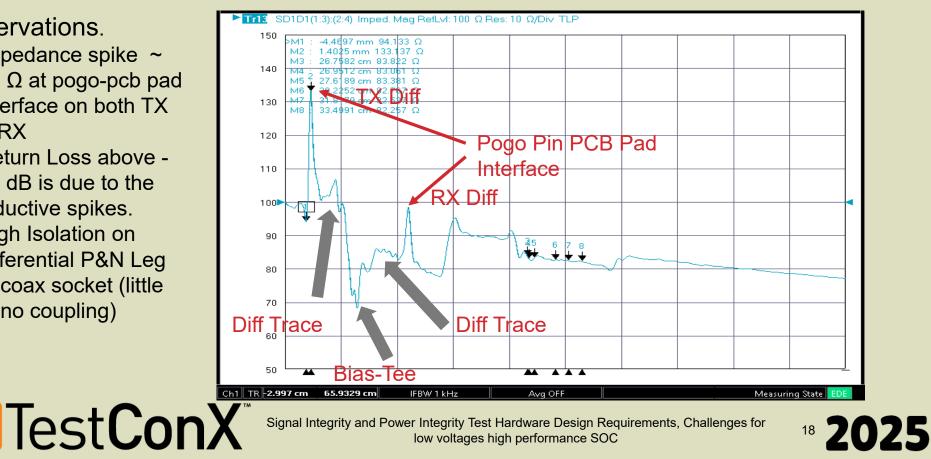

Observations.

- 1. Impedance spike ~ 33  $\Omega$  at pogo-pcb pad interface on both TX & RX

- 2. Return Loss above -10 dB is due to the inductive spikes.

- 3. High Isolation on differential P&N Leg of coax socket (little to no coupling)

Session 3 Presentation 1

Signal Integrity

TestConX Workshop

www.testconx.org

March 2-5, 2025

Signal Integrity

#### Hardware Integration, 3D Physical Modeling

Signal Integrity

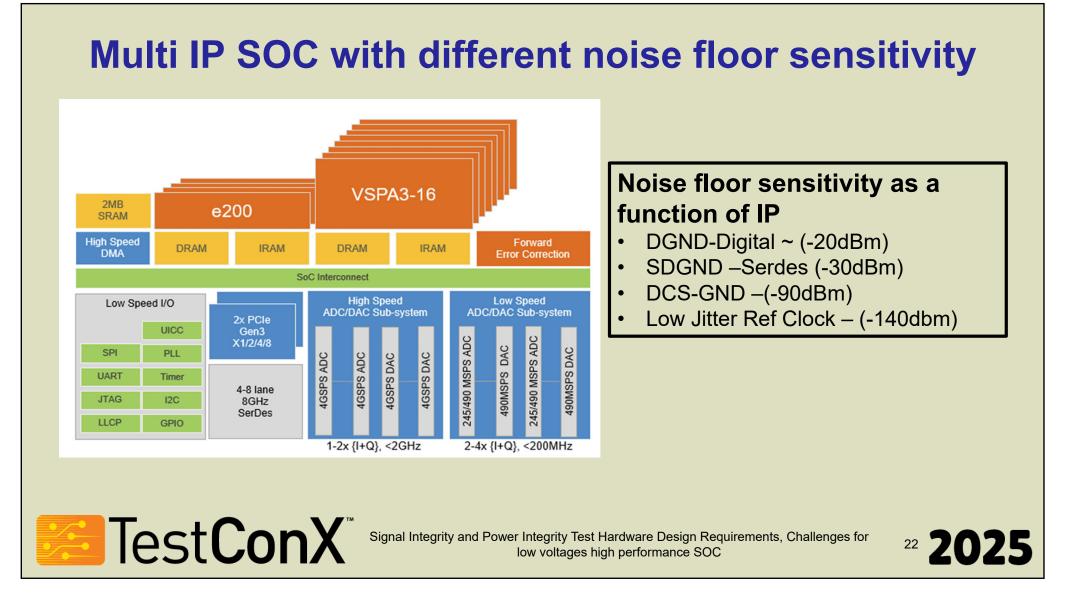

### Noise Floor Sensitivity of Multi-Ip and low voltage SOC

Signal Integrity and Power Integrity Test Hardware Design Requirements, Challenges for low voltages high performance SOC

21

Signal Integrity

Signal Integrity

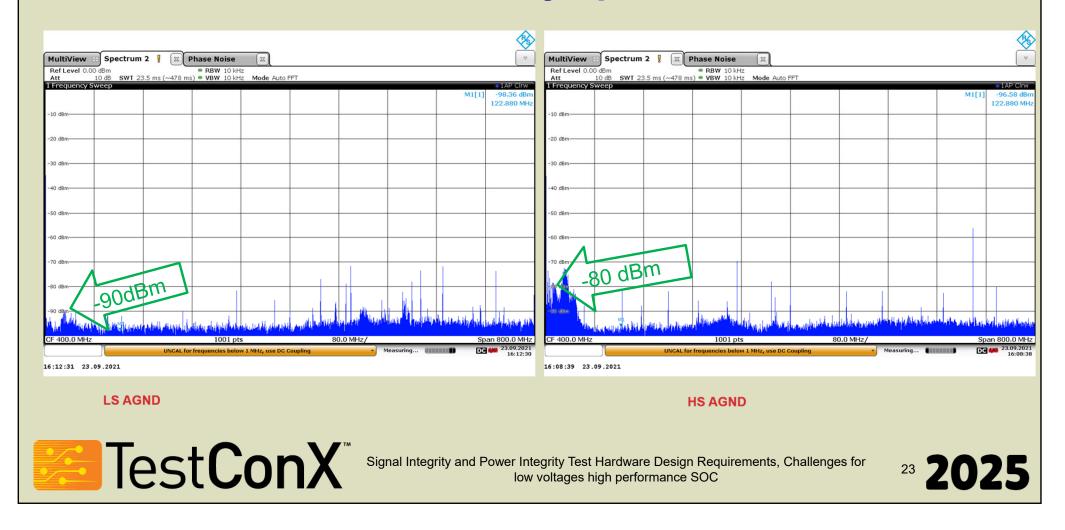

#### **Noise Floor Sensitivity specific to each IP**

Signal Integrity

#### Noise Floor Sensitivity specific to each IP & Associated ATE Instruments

| External Clock 122.88 MHz<br>Frequency Surger<br>Phase Noise = 8.199 Femto Seconds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Ref Level 0.00 dbm<br>10 db SWI 23.5 ms (~478)<br>Fractuary SWI 23.5 ms (~478)<br>10 dbm<br>122.880 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20 dem  External PLL GENERATED CLOCK    30 dem  1. 122.88 Mhz    40 dem  2. Format Differential    50 dem  3. Phase Noise = 81.991 femto seconds    60 dem  4. Integration Range = 10 KHz to 20 MHz    60 dem  90 dem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -20 dbm  ATE GENERATED CLOCK    -30 dbm  1. 122.88 Mhz    -40 dbm  2. Format Differential    -40 dbm  3. Phase Noise = 2.071 pico seconds    -50 dbm  4. Integration Range = 10 KHz to 20 MHz    -60 dbm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| F 400.0 MHz 1001 pts 80.0 MHz/ Span 800.0 MHz/ | CF 400.0 MHz  1001 pts  80.0 MHz/  Span 800.0 MHz    UNCAL for frequencies below 1 MHz, use DC Coupling  Measuring  Image: Comparison of the compar |

| TestConX <sup>™</sup> Signal Integrity and Power In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ntegrity Test Hardware Design Requirements, Challenges for<br>w voltages high performance SOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Signal Integrity

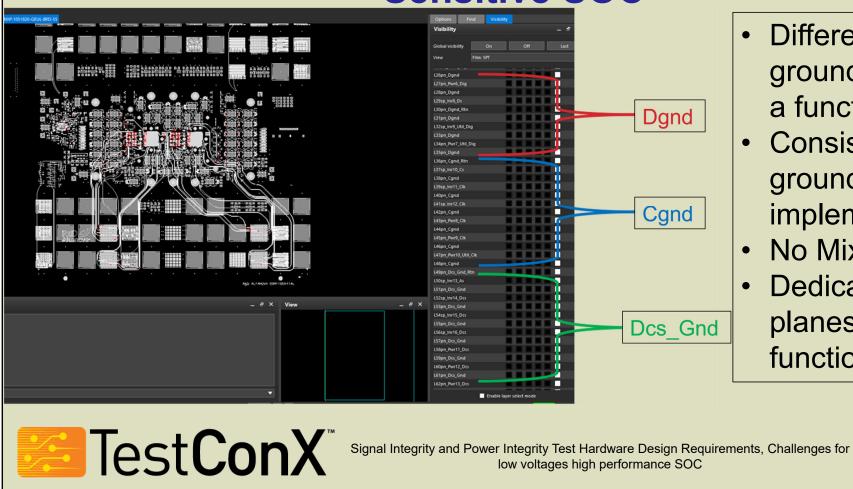

#### **Power, Ground Management for Noise Floor Sensitive SOC**

- Different power, ground domain as a function of IP.

- Consistency in ground, domain implementation.

- No Mixed-ground.

- **Dedicated Power** planes as a function of IP.

<sup>25</sup> **2025**

# Solutions, Mitigation, future questions

Signal Integrity and Power Integrity Test Hardware Design Requirements, Challenges for low voltages high performance SOC

26

Signal Integrity

#### Low Voltage High Performance SOC test hardware implementation

- High Layer count 80 Layers +, Thick PCB 300 mils +.

- Connector, socket impedance-resistance specifications will be challenged to meet single digit parameters.

- Design NRE is considerable addition to cost.

- Hardware 3D, Physical Modeling is more critical than ever. Transmission Line-segment integration is a must.

- Dedicated Power, Ground, Domain management is key to meet SI, and Noise floor requirements (Analog).

- Mechanical (50%) and Electrical (50%) aspect of the Design.

Signal Integrity and Power Integrity Test Hardware Design Requirements, Challenges for low voltages high performance SOC

Signal Integrity

#### **Credits and Recognition**

- NXP Test Socket team (Riley Horner, Sean Young, Matthew Lauderdale)

- Hardware Development Partners

- Henry Lai, Jacob Neely

Signal Integrity and Power Integrity Test Hardware Design Requirements, Challenges for low voltages high performance SOC

## **Presentation / Copyright Notice**

The presentations in this publication comprise the pre-workshop Proceedings of the 2025 TestConX workshop. They reflect the authors' opinions and are reproduced here as they are planned to be presented at the 2025 TestConX workshop. Updates from this version of the papers may occur in the version that is actually presented at the TestConX workshop. The inclusion of the papers in this publication does not constitute an endorsement by TestConX or the sponsors.

There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

The TestConX logo and 'TestConX' are trademarks of TestConX.