# Connecting Your DUT To Your Tester

Tom Bresnan R&D Altanova / Advantest Group

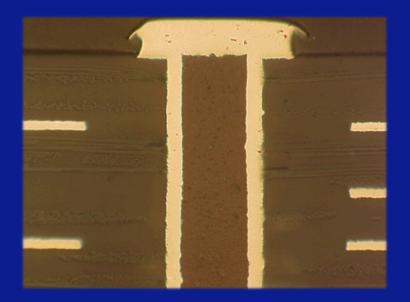

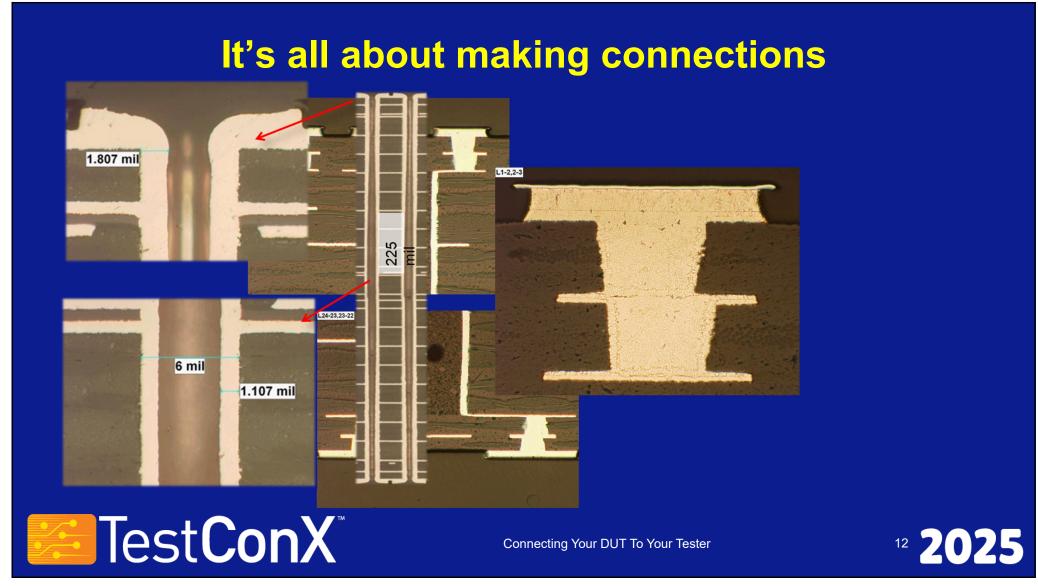

## It's all about making (good) connections

Connecting Your DUT To Your Tester

<sup>3</sup> 2025

TestConX

## It's all about making (good) connections

Connecting Your DUT To Your Tester

4 2025

# It's all about making (good) connections

Connecting Your DUT To Your Tester

**5 2025**

## Why Are We Here?

- What is it?

- How PWB's relate to ATE

- Printed Wiring Boards Automated Test Environment

- Some Attributes

- Materials

- Let's take a break!

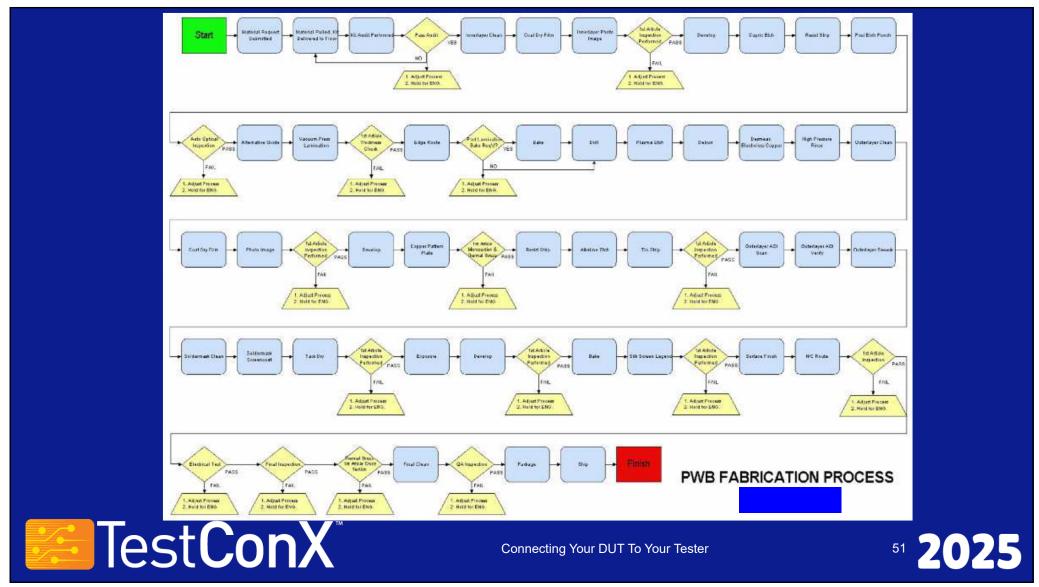

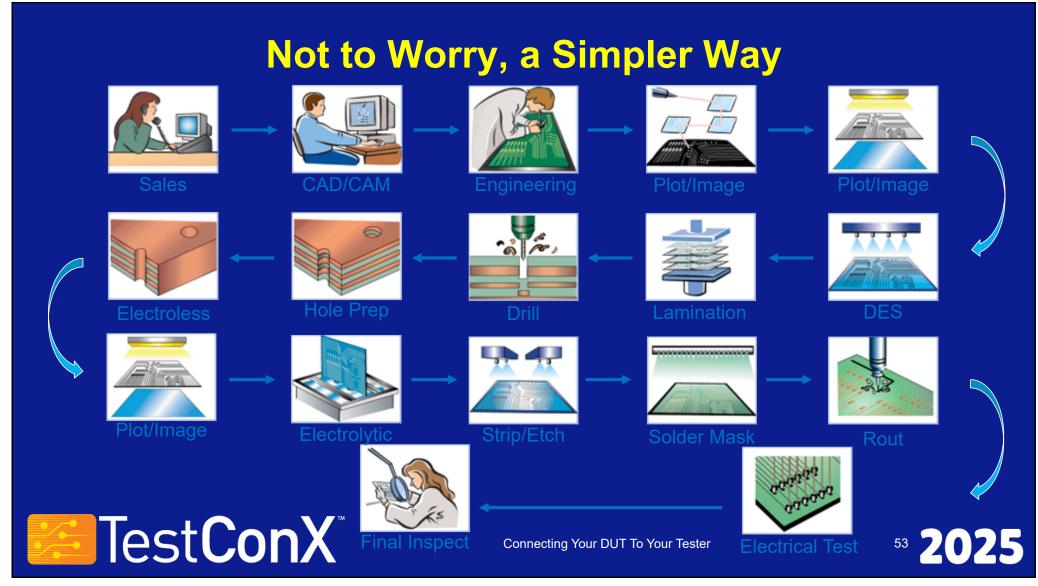

- Process flow and "How's it made?"

- Including some videos of major processes

Connecting Your DUT To Your Tester

2025

#### What's in a Name?

- PWB's

- PCB's

- Printed Circuits Board

- DUT board, DIB, PIB, load board,

#### or ATE board

- Device Interface Board (DIB)

- Probe Interface Board (PIB)

- Interface Board

- Between the <u>Device Under Test and the Tester</u>

Connecting Your DUT To Your Tester

<sup>7</sup> 2025

#### What Is It?

#### Wikipedia

A printed wiring board (PWB) mechanically supports and electrically connects electronic components using conductive tracks, pads and other features etched from copper sheets laminated onto a non-conductive substrate. PWBs can be single sided (one copper layer), double sided (two copper layers) or multi-layer (outer and inner layers). Multi-layer PWBs allow for much higher component density. Conductors on different layers are connected with plated-through holes called vias. Advanced PWBs may contain components - capacitors, resistors or active devices embedded in the substrate.

#### 1980's PWB technology

"PCB Spectrum" by Bill Bertram - Bill Bertram. Licensed under CC BY-SA 3.0 via Commons -

Connecting Your DUT To Your Tester

**8 2025**

#### What Is It?

- Simultaneously, a PWB is:

- Mechanical Device

- Electrical Device

- Thermal Device

Connecting Your DUT To Your Tester

9 2025

#### **PWB Classifications**

- There are two basic ways to form circuits on a PWB

- Additive

- Formation is accomplished by adding copper to a bare PWB, then etching the pattern intended (through ~ 2 oz copper)

- Semi-Additive

- Imaging and plating on top of base copper foil and the unwanted portion of that copper foil is etched away, leaving the desired pattern

- Our discussion today will focus on processes related to the latter method

Connecting Your DUT To Your Tester

<sup>10</sup> **2025**

#### **PWB Classifications**

- Single-sided

- Circuitry on one side only, components installed on back side

- Double-sided

- Circuitry on both sides, plated thru holes, components on one or both sides

- Multilayer

- To increase area for routing, multiple layers may be inside

- Through holes, buried via's or blind via's may be employed to further increase circuit layout density

Connecting Your DUT To Your Tester

**2025**

## The Marketplace

- Worldwide Market 2024

- \$70B

- Estimated to grow to \$90B by 2029

- North American Market 2023

- -~\$12B \$15B

- ATE

- \$1.5B to \$2.5B

- Difficult to estimate

Today's Modern Load Board

Connecting Your DUT To Your Tester

<sup>13</sup> **2025**

## **Measuring Units Used in PWB Industry**

| Units      | Micro<br>Inches | Microns | Mils  | MM       | Inches   | Angstroms   |

|------------|-----------------|---------|-------|----------|----------|-------------|

| Micro Inch | 1               | 0.025   | 0.001 | 0.000025 | 0.000001 | 250         |

| Micron     | 40              | 1       | 0.04  | 0.001    | 0.00004  | 10,000      |

| Mil        | 1000            | 25      | 1     | .025     | 0.001    | 250,000     |

| MM         | 40,000          | 1,000   | 40    | 1        | 0.04     | 100,000,000 |

|            |                 |         |       |          |          |             |

<sup>14</sup> **2025**

#### **Attributes of A PWB & Difficulty Levels**

| Attribute                   | Туре             | Low       | Medium   | High    | ATE     |

|-----------------------------|------------------|-----------|----------|---------|---------|

| Layer Count                 |                  | 2-40      | 40 to 60 | 60+     | 68+     |

| Board<br>Thickness          |                  | 3.2mm     | 5.1mm    | 6.35mm  | 8.0mm+  |

| Aspect Ratio                | Plated Thru Hole | 12:1      | 15:1     | 20:1    | 30+:1   |

|                             | Blind Via        | 2:1       | 1:1      | 0.75:1  |         |

| Line & Space                | Inner Layer      | 100μ/100μ | 75µ/75µ  | 50μ/50μ | 50µ/50µ |

|                             | Outer Layer      | 125μ/125μ | 75µ/75µ  | 50μ/75μ | 50µ/50µ |

| Minimum Drill               |                  | 250µ      | 200µ     | 150µ    | 100µ    |

| Solder Mask<br>Registration |                  | 100μ      | 75µ      | 50µ     |         |

Connecting Your DUT To Your Tester

<sup>5</sup> 2025

#### **Attributes of A PWB (in inches)**

| Attribute                   | Туре             | Low         | Medium      | High        | ATE         |

|-----------------------------|------------------|-------------|-------------|-------------|-------------|

| Layer Count                 |                  | 2-40        | 40 to 60    | 60+         | 68+         |

| Board<br>Thickness          |                  | 0.126       | 0.200       | 0.250       | 0.320+      |

| Aspect Ratio                | Plated Thru Hole | 12:1        | 15:1        | 20:1        | 30+:1       |

|                             | Blind Via        | 2:1         | 1:1         | 0.75:1      | n/a         |

| Line & Space                | Inner Layer      | 0.004/0.004 | 0.003/0.003 | 0.002/0.002 | 0.002/0.002 |

|                             | Outer Layer      | 0.005/0.005 | 0.003/0.003 | 0.002/0.003 | 0.002/0.002 |

| Minimum Drill               |                  | 0.010       | 0.008       | 0.006       | 0.004       |

| Solder Mask<br>Registration |                  | 0.004       | 0.003       | 0.002       |             |

Connecting Your DUT To Your Tester

<sup>16</sup> **2025**

#### **Attributes of a Device**

- Pitch

- Device, trace, space, hole to copper

- Layers

- Rows on a BGA device

- Hole Diameter

- Function of device pitch

- Aspect Ratio

- Ratio of thickness to hole diameter (think soda straw)

Photo credit: 1stretroshop.com

Connecting Your DUT To Your Tester

<sup>17</sup> **2025**

## **Attributes – By Device Pitch**

- 1.0mm, 0.8mm, 0.5mm, 0.4mm ....

- Translates to other attributes

- Line width

- Spacing

- Dielectric spacing

- Hole to copper feature dimensions

To Your Tester 18 **2025**

## **Attributes by Device Pitch**

|               | 1.0mm (0.0394)         | 0.8mm (0.0315)             | <b>0.5mm</b> (0.0197)     | <b>0.4</b> mm (0.0157)   |

|---------------|------------------------|----------------------------|---------------------------|--------------------------|

| Pad           | <b>0.76mm</b> (0.0299) | 0.66mm<br>(0.026)          | 0.35mm<br>(0.0138)        | 0.3mm<br>(0.0118)        |

| Hole          | 0.37mm<br>(0.0146)     | 0.3mm<br>(0.0118)          | 0.15mm<br>(0.0059)        | <b>0.1mm</b> (0.0039)    |

| Line          | 200µ<br>(0.008)        | 200µ/125µ<br>(0.008/0.005) | 200µ/75µ<br>(0.008/0.003) | 200µ/50µ<br>0.008/0.002) |

| Hole 2 Copper | <b>0.25mm</b> (0.010)  | 0.18mm<br>(0.007)          | 0.12mm<br>(0.005)         | <b>0.1mm</b> (0.004)     |

| Aspect Ratio  | Low                    | Medium                     | High                      | Extreme                  |

Connecting Your DUT To Your Tester

<sup>19</sup> **2025**

## **Hole to Copper Dimensions**

Connecting Your DUT To Your Tester

<sup>20</sup> **2025**

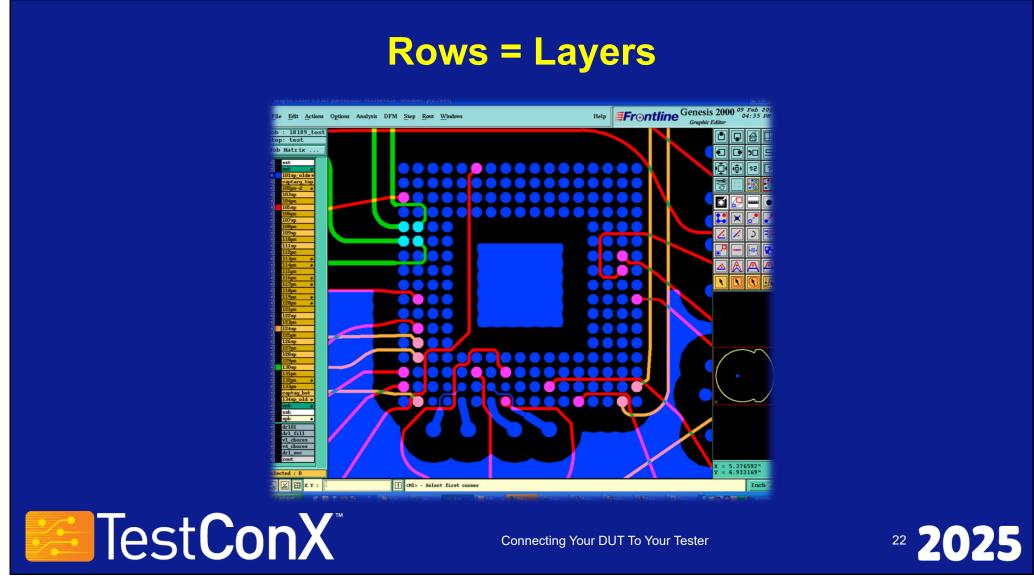

## **Attributes - Layers**

- Each row of a BGA device = one signal layer

- Signal layers need corresponding ground planes

- Impedance control

- May need additional routing layers

<sup>21</sup> **2025**

#### **Attributes – Hole Diameter**

- Drilled or finished hole diameter

- Human Hair

- $-40\mu$  to 250 $\mu$  (0.0015" to 0.010")

- $-100\mu$  is pretty average (0.004")

- Today's interface boards are drilled with a 100µ to 150µ drill bit (0.004" to 0.006")

- And smaller

<sup>23</sup> **2025**

## **Attributes – Aspect Ratio**

- Ratio of the board thickness relative to drilled hole diameter

- 1.0mm device, 13:1

- 0.8mm device, 16:1

- 0.5mm device, 31:1

- 0.4mm device, 38:1

- 0.35mm device, >40:1

ter 24 **2025**

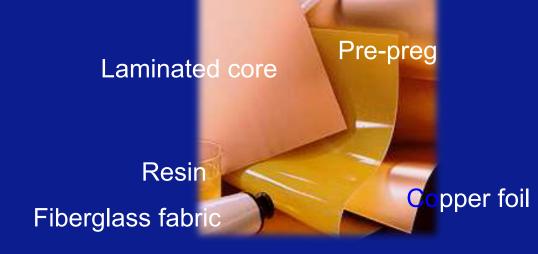

#### **Let's Talk About Materials**

Wikipedia...A printed circuit board, or PCB, is used to mechanically support and electrically connect electronic components using conductive pathways, on a nonconductive substrate.

Connecting Your DUT To Your Tester

Photo courtesy of Isola

<sup>25</sup> **2025**

#### **Materials & More**

Material properties are playing an increasingly important role in advanced board designs as speed, power dissipation, signal fidelity and process temperatures increase

Factors that influence material selection

Electrical Design:

Dielectric constant

Loss tangent

Reliability: Assembly process Long-term life Thermal/Mechanical: X, Y, Z CTE Conductive cooling

Connecting Your DUT To Your Tester

<sup>26</sup> **2025**

#### **Laminates**

- Pre-preg

- Fiberglass cloth (woven)

- Resin

- Copper foil

- Electrodeposited (ED)

Connecting Your DUT To Your Tester

Photo courtesy of Isola

<sup>27</sup> **2025**

## Why Copper?

- Copper is an excellent electrical conductor

- Low electrical resistivity

- Inexpensive metal

- Soft and easily workable

- Easily processed

- Patternable by photolithography

- Using relatively benign chemistry

Connecting Your DUT To Your Tester

28 2025

## **Copper Foil**

- Copper is the dominant metal for interconnection use

- Specified by weight

- $-\frac{1}{2}$  ounce per square foot

- 1 ounce per square foot

- Corresponding thicknesses

- 17u and 35u respectively

- Usually produced by electrolytic deposition on a mandril

- 99.8% purity common

- Thickness tolerance is approx. 10%

Connecting Your DUT To Your Tester

<sup>29</sup> **2025**

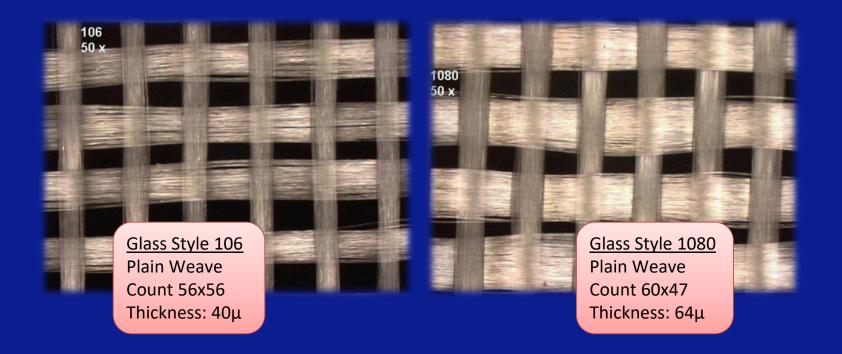

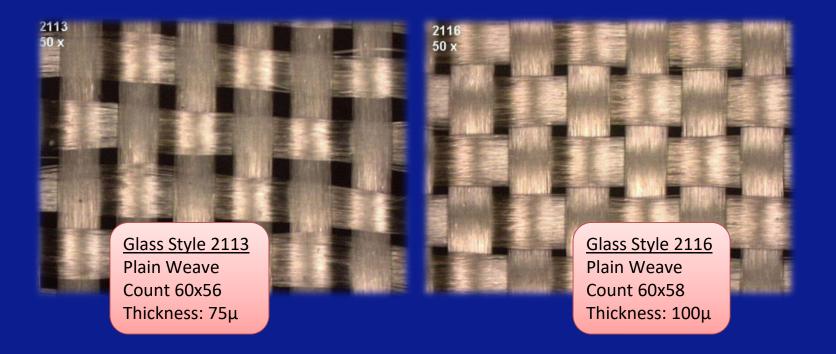

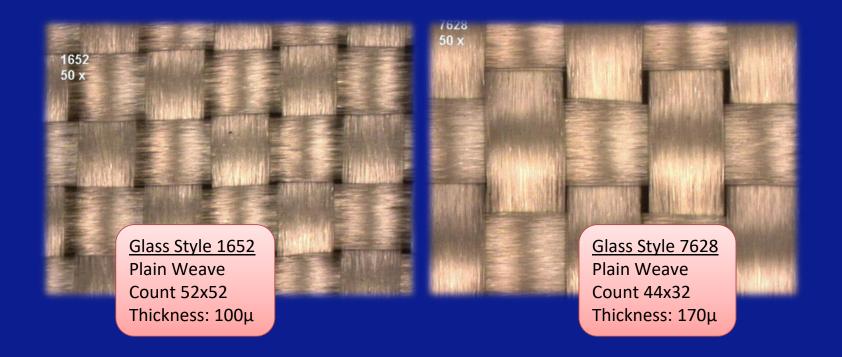

## Materials – 'Pre-Preg'

Connecting Your DUT To Your Tester

Photos courtesy of Isola

2025

## Materials - 'Pre-Preg'

Connecting Your DUT To Your Tester

Photos courtesy of Isola

2025

## Materials - 'Pre-Preg'

Connecting Your DUT To Your Tester

Photos courtesy of Isola

2025

#### Laminate

- Enhanced FR-4's

- Modified Epoxies

- Teflon

- BT

- Polyimide

- Hybrid

- Too many to do justice to each supplier

Connecting Your DUT To Your Tester

<sup>3</sup> 2025

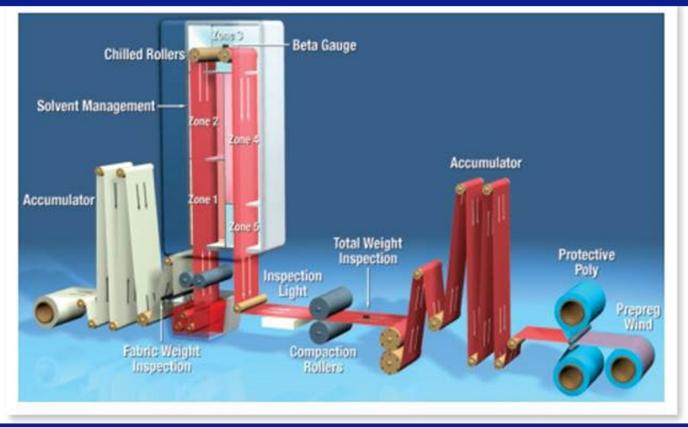

## **Pre-Preg - how it's made**

Connecting Your DUT To Your Tester

<sup>34</sup> **2025**

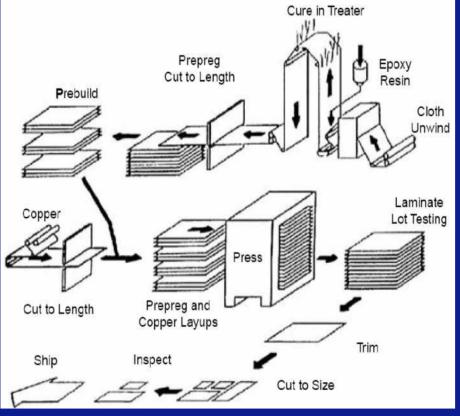

#### **Laminate Process Flow**

Connecting Your DUT To Your Tester

<sup>35</sup> **2025**

TestConX 2025 Tutorial 2

## **Laminate – How It's Made**

Connecting Your DUT To Your Tester

<sup>36</sup> **2025**

TestConX

TestConX 2025 Tutorial 2

### **Laminate – How It's Made**

Connecting Your DUT To Your Tester

<sup>37</sup> **2025**

TestConX

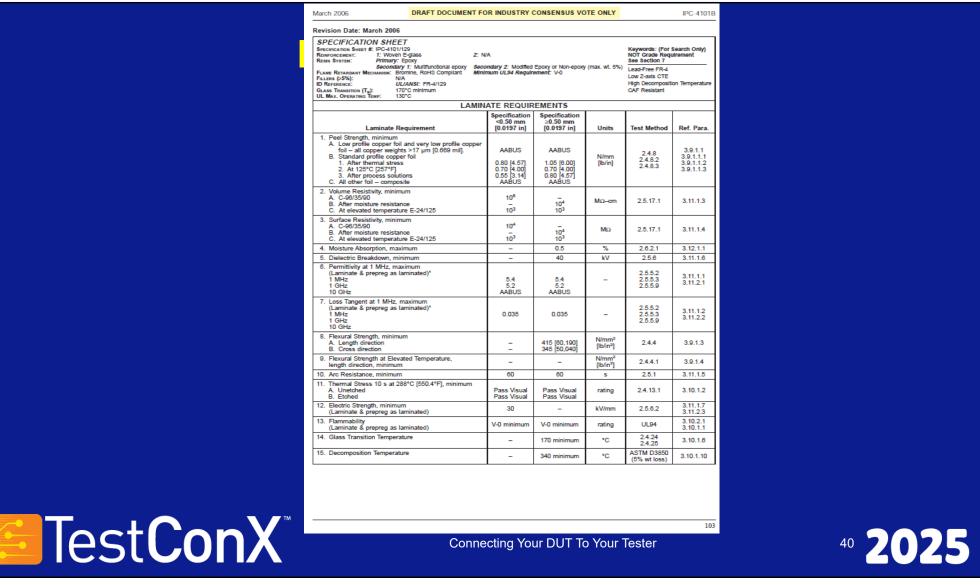

## **Laminate Construction (caveat emptor)**

| Thickness | Tolerance | Construction       | Resin<br>Content | E <sub>r</sub> @<br>1 MHz | E <sub>r</sub> @<br>10 GHz |  |

|-----------|-----------|--------------------|------------------|---------------------------|----------------------------|--|

| 0.008     | 0.001     | 1x 7628            | 44.4%            | 4.55                      | 4.12                       |  |

| 0.008     | 0.001     | 2x 2116            | 43.0%            | 4.54                      | 4.11                       |  |

| 0.008     | 0.001     | 1x 2116<br>1x 2113 | 48.6%            | 4.36                      | 4.02                       |  |

| 0.008     | 0.001     | 1x 7629            | 42.6%            | 4.38                      | 4.12                       |  |

Connecting Your DUT To Your Tester

<sup>38</sup> **2025**

### **Laminate Construction**

- Know what you're getting

- Understand the implications

- Electrically significant or not

- Mechanically significant!

Connecting Your DUT To Your Tester

# **Material Properties**

- Mechanical and Thermal

- Peel strength

- X-Y CTE

- Z CTE

- Tg

- DSC

- TMA

- DMA

Connecting Your DUT To Your Tester

<sup>41</sup> **2025**

### **Material Properties**

- Electrical

- Dielectric Constant or

- ε<sub>r</sub> Epsilon-sub-r (or relative permittivity)

- The dielectric constant is a ratio of the capacitance of a capacitor in which a particular insulating material is the dielectric, to the capacitance of the capacitor in which a vacuum is the dielectric.

- Also known as E-sub-r

- Effective Permittivity

<sup>42</sup> **2025**

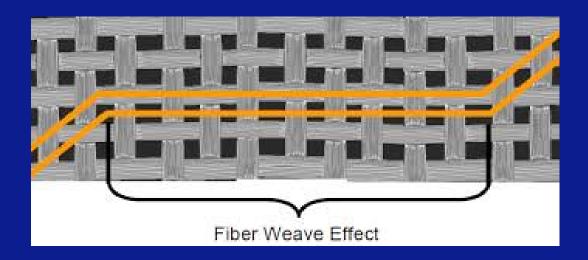

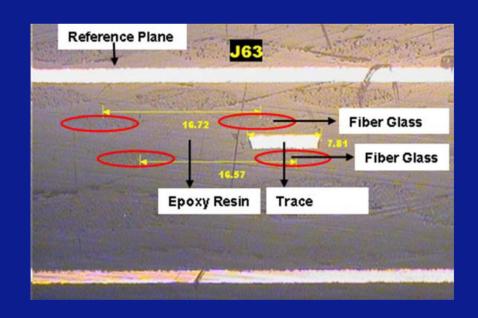

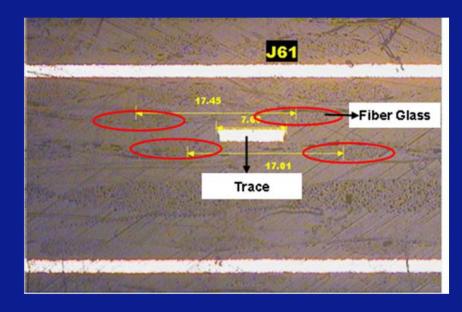

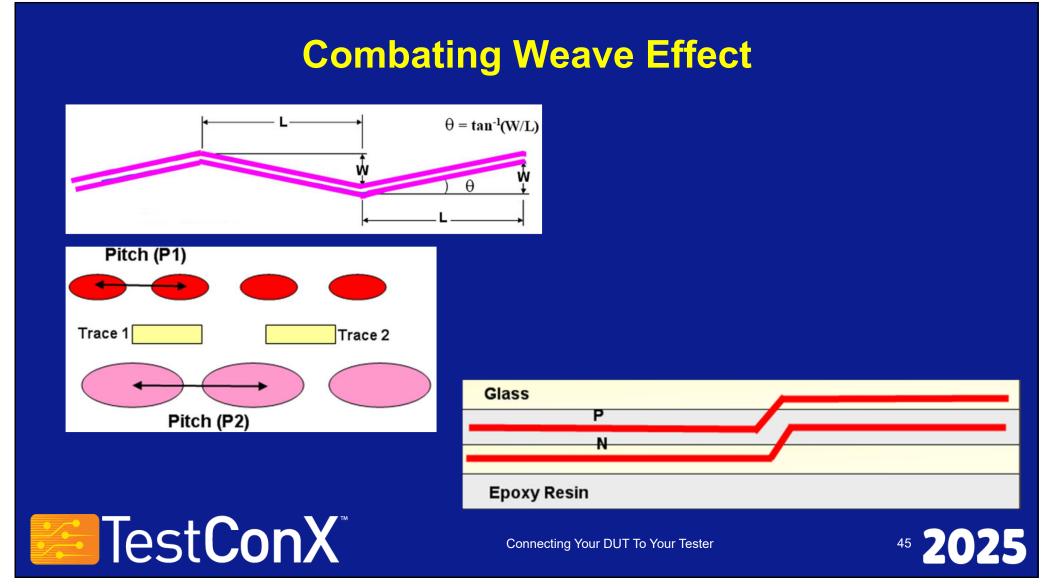

### **Material Properties – Weave Effect**

Connecting Your DUT To Your Tester

<sup>43</sup> **2025**

### **Material Properties – Weave Effect**

Connecting Your DUT To Your Tester

<sup>44</sup> **2025**

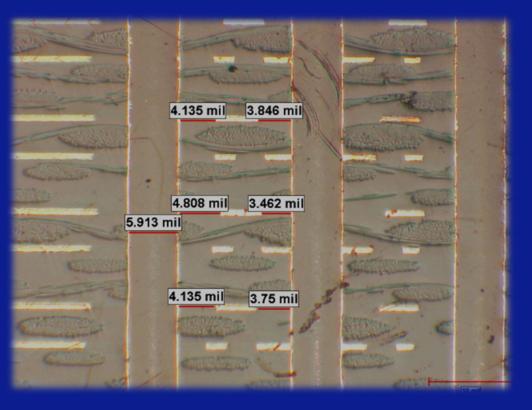

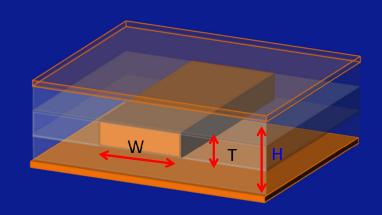

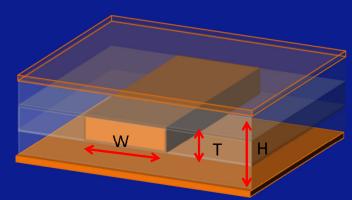

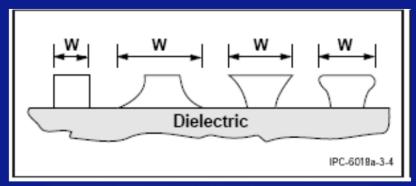

### **Material Properties – Trace Variabilities**

- Dry film etch tolerance is +/-12µ;

therefore as W decreases Z0 error increases.

- As H decreases, tolerance changes from +/- 10% to ~+/-15μ. H also varies within a sheet +/- 10μ.

- T does not vary significantly, but a 'tall' T results in higher resin flow around the trace and makes the final thickness H somewhat less predictable.

- A 'tall' T is also prone to under etch, which influences Z0.

• Fiberglass reinforced materials are not homogenous, and  $\epsilon_r$  is not constant in the material.

\*Z0 or Z naught = impedance

Connecting Your DUT To Your Tester

<sup>46</sup> **2025**

## **Material Properties – Trace Variabilities**

• Important: driven by etch variation and by heterogeneous materials Z0 varies as a function of distance.

| 100um example in 1/2 Oz copper: |        |         |        |  |  |  |  |  |

|---------------------------------|--------|---------|--------|--|--|--|--|--|

| Trace Etch Width                |        |         |        |  |  |  |  |  |

|                                 | min    | nominal | max    |  |  |  |  |  |

|                                 | 88 um  | 100 um  | 112 um |  |  |  |  |  |

|                                 | 53.2 Ω | 50.1 Ω  | 47.4 Ω |  |  |  |  |  |

|                                 |        |         |        |  |  |  |  |  |

| Height                          | Height |         |        |  |  |  |  |  |

|                                 | min    | nominal | max    |  |  |  |  |  |

|                                 | 201 um | 223 um  | 245 um |  |  |  |  |  |

|                                 | 47.0 Ω | 50.1 Ω  | 53.0 Ω |  |  |  |  |  |

|                                 |        |         |        |  |  |  |  |  |

| Combined Error                  |        |         |        |  |  |  |  |  |

|                                 | min    | nominal | max    |  |  |  |  |  |

|                                 | 44.3 Ω | 50.1 Ω  | 56.1 Ω |  |  |  |  |  |

|                                 |        |         |        |  |  |  |  |  |

Connecting Your DUT To Your Tester

<sup>47</sup> **2025**

|                  | Materials Chart |               |               |               |        |                |              |                |              |                |              |                |

|------------------|-----------------|---------------|---------------|---------------|--------|----------------|--------------|----------------|--------------|----------------|--------------|----------------|

|                  | Mwave<br>1000   | Mwave<br>2000 | Mwave<br>3000 | Mwave<br>4000 | Meg 6  | Rogers<br>4350 | N4000-<br>13 | N4000-<br>13SI | N4800-<br>20 | N4800-<br>20SI | Astra<br>MT7 | Tachyon<br>100 |

| Mech             |                 |               |               |               |        |                |              |                |              |                |              |                |

| Peel<br>strength |                 |               |               |               |        |                |              |                |              |                |              |                |

| After float      | 6.6             | 6.6           | 5.5           | 5.5           | .8kN/m | 5              | 7.5          | 7.5            | 7            | 7              | 5.7          |                |

| At elev.<br>temp | 5.6             | 5.6           | 4.4           | 4.4           | n.a.   | n.a.           | 8.1          | 8.1            | 6.5          | 6.5            | n.a.         | 5.5            |

| After exp./proc  | 5.3             | 5.3           | 5             | 5             | n.a.   | n.a.           | 9            | 9              | 7            | 7              | n.a.         | 5.5            |

| X-Y CTE          | 10-14           | 10-14         | 10-14         | 10-14         | 14-16  | 10-12          | 10-14        | 10-14          | 10-14        | 10-14          | 12           | 15             |

| Z CTE<br>α1      | 55              | 55            | 55            | 55            | 45     | 32             | 70           | 70             | 27           | 31             | 60           | 45             |

| Z CTE<br>α2      | 260             | 260           | 260           | 260           | 260    | n.a.           | 280          | 280            | 205          | 210            | 300          | 250            |

α1, 50C to Tg; α2, Tg to 260C

Connecting Your DUT To Your Tester

<sup>48</sup> **2025**

#### **Materials Chart Mwave** Meg 6 N4000 N4000 N4800 N4800 Mwave Mwave Mwave Rogers **Astra Tachyon** 1000 2000 3000 4000 -13 **-13SI** -20 -20SI MT7 4350 100 **Electrical** Dk 2 Ghz 3.7 3.7 3.2 3.7 3.4 3.8 3.5 3.71 3.55 3 3.04 n.a. 10 Ghz 3.7 3.4 3.8 3.5 3.61 3.48 3.7 3.3 3.8 3.4 3 3.02 Df 2 Ghz 0.003 0.0032 0.002 0.002 0.0031 0.009 0.008 0.007 0.0055 0.0017 0.004 0.0021 10 Ghz 0.0048 0.0075 0.0017 0.0055 0.004 0.0028 0.004 0.0037 0.008 0.007 0.006 0.0021 **Thermal** (Tg) **TMA** 215 215 170 170 280 200 200 180 180 180 n.a. n.a. DMA 240 240 240 210 210 220 200 200 210 n.a. 240 n.a. DSC 185 210 210 200 200 200 185 n.a. n.a. n.a. n.a. n.a.

DSC, Differential Scanning Calorimetry; TMA, Thermomechanical Analysis; DMA, Dynamic Mechanical Analysis.

Connecting Your DUT To Your Tester

<sup>49</sup> **2025**

### **Before We Continue to The Process**

Connecting Your DUT To Your Tester

# The Process – Inner Layer Imaging

- Photo resist application

- UV Exposure

- Laser Direct Imaging (LDI)

- Collimated light & film

- Polymerizes resist

- Develop

- Removes non-polymerized resist

Connecting Your DUT To Your Tester

<sup>55</sup> **2025**

## The Process – Inner Layer Imaging

- Photo resist application

- UV Exposure

- Laser Direct Imaging (LDI)

- Collimated light & film

- Polymerizes resist

- Develop

- Removes non-polymerized resist

Connecting Your DUT To Your Tester

<sup>56</sup> **2025**

# The Process – Inner Layer Imaging

- Photo resist application

- UV Exposure

- Laser Direct Imaging (LDI)

- Collimated light & film

- Polymerizes resist

Removes non-polymerized resist

Connecting Your DUT To Your Tester

<sup>57</sup> 2025

## The Process – Inner Layer Imaging

- Etch & Strip

- Removal of base copper

- Non-polymerized area

- Various chemistries available

- Ammonia based

- Cupric chloride based

- Resist removal

Connecting Your DUT To Your Tester

<sup>58</sup> **2025**

# The Process – Automatic Optical Inspection

### Post-Etch Punch

- Registers all layers to common optical targets

- Slots added for tooling purposes

#### AOI

- Data downloaded from CAM

- Core layer scanned

- Compared to CAM data

- Verification

Connecting Your DUT To Your Tester

<sup>59</sup> **2025**

### **The Process – Oxide Treatment**

- Copper Surface Preparation

- Adhesion promotion

- Added bonding strength

- Reduced oxide

- Pink ring elimination

- Alternative oxide

- Variety of materials

- Multiple or sequential laminations

Connecting Your DUT To Your Tester

## The Process – Layup & Lamination

- Registration and stacking of cores

- Process combines cores, pre-preg and copper foil

- Multiple times thru this process may be required

- Simple thru-hole vs. sequential lamination

- Pin lamination

- Registration or layer to layer alignment

- Vacuum chamber

- Heat, pressure, time

- Tightly controlled process window

Connecting Your DUT To Your Tester

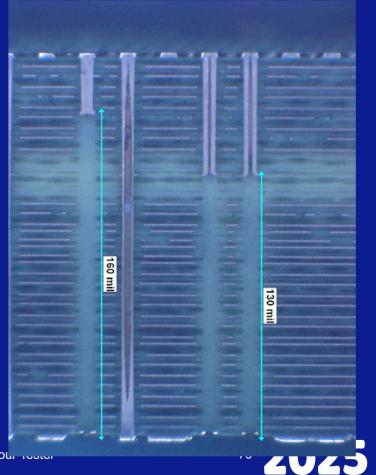

### **The Process - Drill**

- Mechanical hole formation

- $-100\mu 150\mu$  typical

- Opto-mechanical positioning

- Glass scales

- Real-time drill bit analysis

- Diameter

- Run-out

- Broken bit detection

- Stub drilling or back drilling

Connecting Your DUT To Your Tester

### **The Process - Drill**

- Laser hole formation

- Microvias down to 25µ

- Opto-mechanical positioning

- Blind vias

- Buried vias

Connecting Your DUT To Your Tester

<sup>64</sup> **2025**

# The Process – Hole Prep & Copper Plate

- Desmear

- Removes epoxy smear from interconnects

- Created during drill operations

- Chemical removal

Connecting Your DUT To Your Tester

# The Process – Hole Prep & Copper Plate

- Etchback

- Different from desmear

- Removes epoxy resin from dielectric space

- May include a glass etch

- Three point connection

- Some materials resistant to previous chemical process

Connecting Your DUT To Your Tester

## The Process – Hole Prep & Copper Plate

- Electroless copper deposition

- Seed layer

- Prepares dielectric and interconnects for subsequent plating operations

- 30 micro-inches 40 micro-inches followed by copper plating

- 75 micro-inches 125 micro-inches to prep for imaging process

- Unfriendly chemistry

- Inherently unstable

Connecting Your DUT To Your Tester

<sup>67</sup> **2025**

### The Process – Hole Prep & Copper Plate

- Carbon

- Graphite

- Palladium

- Electroless Nickel

- Conductive Polymer

- Non-Formaldehyde-Based Electroless Copper

Connecting Your DUT To Your Tester

### The Process – Hole Fill

- Fill to create flat surface

- Needed for socket touchdown

- Vacuum assist

- High aspect ratio

- Blind vias

Connecting Your DUT To Your Tester

### **The Process - Planarization**

- Fill to create flat surface

- Needed for socket touchdown

- Vacuum assist

- High aspect ratio

- Blind vias

- Planarize the surface

<sup>70</sup> **2025**

# The Process – Outer Layer Imaging

- Reversed from inner layer imaging

- Plating resist, not etch resist

- Photo-resist application

- UV Exposure

- Film and collimated light

- LDI or Laser Direct Imaging

- Polymerizes photo-resist

- Develop

- Removal of non-polymerized resist

Connecting Your DUT To Your Tester

<sup>71</sup> **2025**

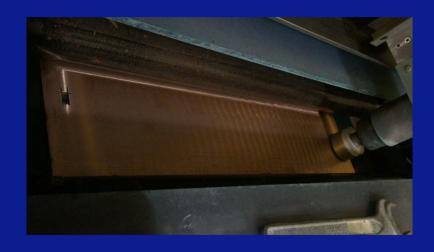

# The Process – Copper-Nickel-Gold Plating

- Electroplating

- Chemistry (electrolyte solution)

- Power rectifier

- Rectifier converts AC to DC

- Anode (copper)

- Cathode (PWB panel)

<sup>72</sup> **2025**

TestConX 2025 **Tutorial 2**

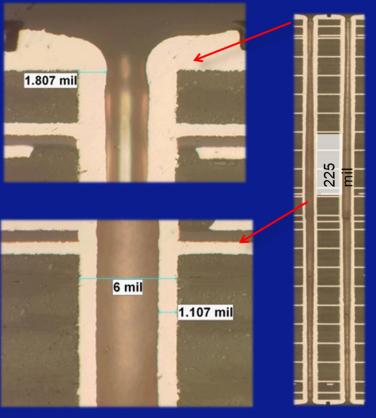

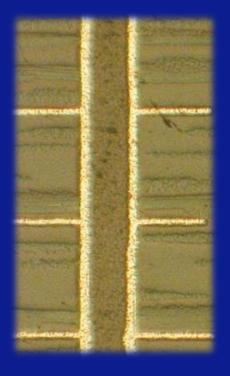

### The Process – Copper-Nickel-Gold Plating

1 mil (25 micron) minimum copper thickness in holes

Minimize surface buildup

- Aspect ratio

- Through holes or microvias

- Robust and survivable

- Etch resist

Connecting Your DUT To Your Tester

73 **2025**

TestConX

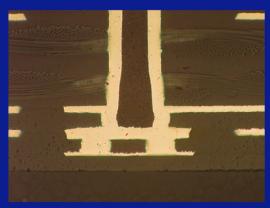

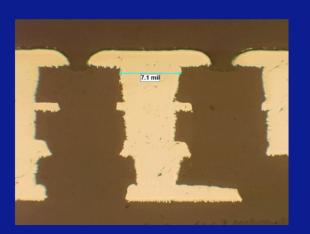

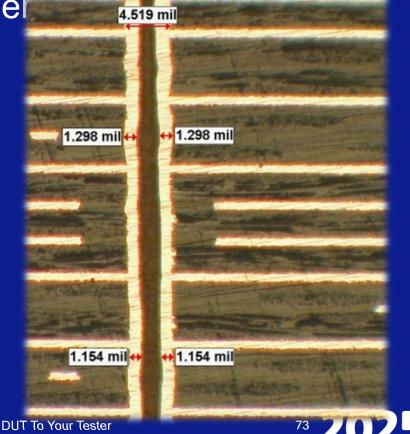

### The Process – Outer Layer Etch

- Define the outer layer(s) pattern

- Removal of base copper

- Defines lines, pads, other features

- Impedance control

- Nickel / Hard Gold typical ATE finish

- Etch factors and 'overhang'

- Other finishes available

Connecting Your DUT To Your Tester

<sup>74</sup> **2025**

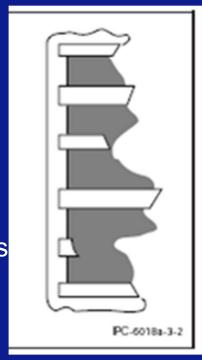

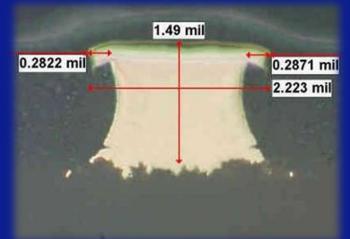

### **The Process – Outer Layer Etch**

- Overhang

- Depends on surface finish

- 1:1 thickness

- Surface thickness critical

Test Con X

Connecting Your DUT To Your Tester

<sup>75</sup> **2025**

March 2-5, 2025

TestConX

#### The Process – Electrical Test

- Direct measurement for first board

- Indirect measurement of subsequent boards

- Isolation and continuity

- Capacitive or electromagnetic coupling

- Broken traces = reduced coupling

- Shorted traces = increased coupling

- Trace to ground (increased degree of confidence)

- Adjacency analysis

Connecting Your DUT To Your Tester

<sup>76</sup> **2025**

#### The Process – Solder Mask

- Epoxy based coating

- Available in colors and clear

- Surface protection

- Solder resist, as the name implies

- Product identification

- Liquid Photo-imageable

- Spray coated or screen flood

- Dry film still in use

Connecting Your DUT To Your Tester

<sup>7</sup> 2025

### The Process – Silk Screen or Legend

- Assembly nomenclature or legend

- Available colors

- Product identification

- Screen print

- Inkjet

To Your Tester 78 **2025**

## The Process - Depanelization

- Secondary Drill (non-plated holes)

- Back drill or stub drill

- Counterbores / countersinks

- Slots

- Routing

Connecting Your DUT To Your Toxor

### The Process – Final Inspection

- Visual and dimensional

- Cosmetic defects

- Impedance testing

- Cross sections

- Other measurements and certifications

80 **2025**

#### May this information help you weather your PWB storms

https://www.pinterest.com/source/ anchorcharters.com.au/

TestConX<sup>®</sup>

Connecting Your DUT To Your Tester

<sup>81</sup> **2025**

TestConX March 2-5, 2025

#### About Us – R&D Altanova

- Founded in 1969

- Part of the Advantest Group AAI since 2021

- Full Turn-Key Supplier

- SI/PI Engineering

- Mechanical Engineering

- Design & Layout

- Fabrication (US & Taiwan)

- Assembly

- Sockets and Interconnects spring probe & elastomer

Connecting Your DUT To Your Tester

82 **2025**

#### **Thank You!**

• Tom Bresnan — tom.bresnan@rdaltanova.com — 732-549-4554 x3110

Visit our website – www.rdaltanova.com

TestConX

Connecting Your DUT To Your Tester

83 **2025**

# **Presentation / Copyright Notice**

The presentations in this publication comprise the pre-workshop Proceedings of the 2025 TestConX workshop. They reflect the authors' opinions and are reproduced here as they are planned to be presented at the 2025 TestConX workshop. Updates from this version of the papers may occur in the version that is actually presented at the TestConX workshop. The inclusion of the papers in this publication does not constitute an endorsement by TestConX or the sponsors.

There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

The TestConX logo and 'TestConX' are trademarks of TestConX.