1

TestConX Korea Workshop

TestConX.org

# Contents

- importance of reliability to semiconductor business

- how to burn-in(as-is)

- baseline cost of burn-in

- strategy to make it more efficient

- ideal arrange

- next challenge

Space-Efficient Wafer Level Burn-In tool

2

TestConX.org

# importance of reliability

- basically: to screening infant failure of mass production

- HBM: additive structure, lot of connection

- power device: simpler function, required highly reliability •

- when deforms, crack or void comes to sub-micro level, inspection could be more expensive than burn-in

TestConX Korea Workshop

TestConX.org

- only two things needed to burn-in space and time

- 1. where to place a wafer?

- 2. what/when/where is this happen?

- **1 prober**'s capacity **7 days** / 10 hours = 16.8 wafer/week

- to produce **100 wafers** a week, 10 hours x 100 wafer = 1 000 wafer-hours

- required number of tool, 1 000 wafer-hours / 16.8 = 60 probers

- 60 probers footprint = very large

Space-Efficient Wafer Level Burn-In tool

Δ

TestConX.org

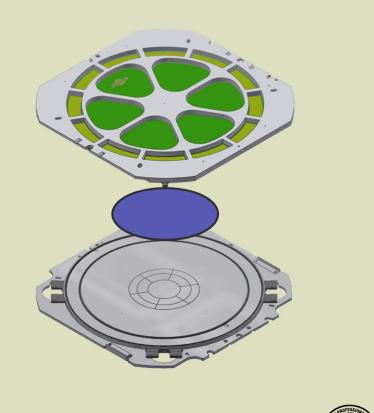

#### structure of TCS

- 3 things those required to burn-in

- 1. alignment; probe card with wafer, also probe card with tester

- 2. contact; probe card with wafer, also probe card with tester

- 3. burn-in; execute pgm under controlled thermal, electrical circumstance

Space-Efficient Wafer Level Burn-In tool

TestConX Korea Workshop

TestConX.org

Session 2 Presentation 2

6

TestConX Korea Workshop

TestConX.org

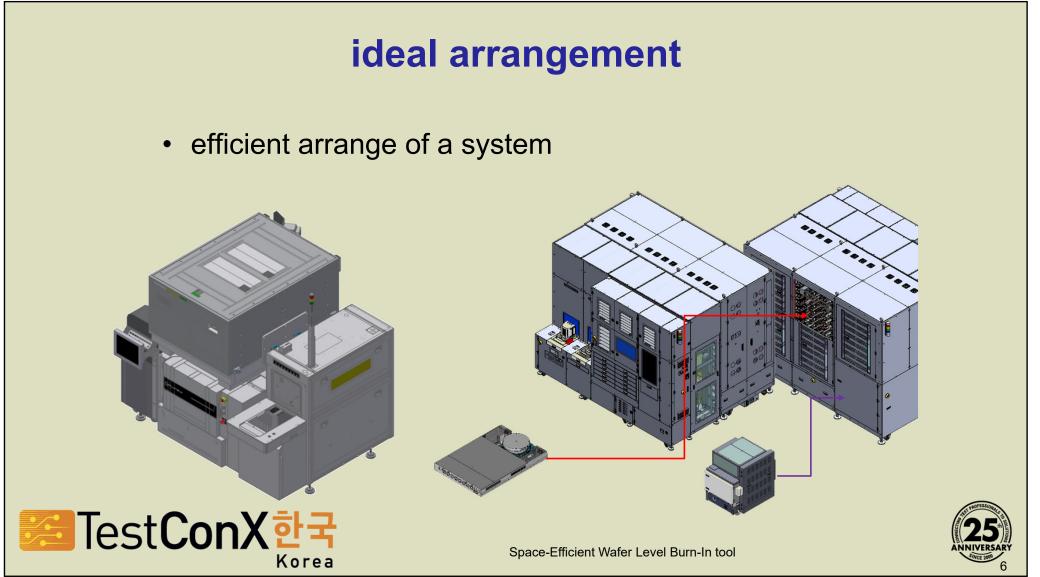

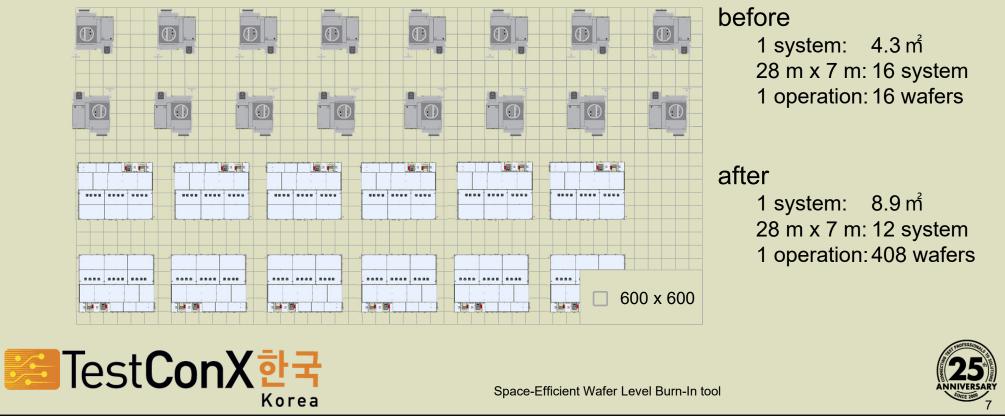

#### • efficient arrange of a system

7

TestConX.org

# additional function

- individual process simple and easy to manage lot

- fully automated less man-hour, less idle time

- cost of ownership

### upcoming challenges

- developing tester to be capable for final test

- developing smaller tester, to achieve higher density

- · developing tester capability for more kind of device

Space-Efficient Wafer Level Burn-In tool

TestConX.org

# **Presentation / Copyright Notice**

- The presentations in this publication comprise the pre-workshop Proceedings of the TestConX Korea workshop. They reflect the authors' opinions and are reproduced here as they are planned to be presented at TestConX Korea. Updates from this version of the papers may occur in the version that is actually presented at TestConX Korea. The inclusion of the papers in this publication does not constitute an endorsement by TestConX or the sponsors.

- There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

- The TestConX logo, 'TestConX', and 'TestConX Korea' are trademarks of TestConX.