# **TestConX**<sup>\*</sup>

## Archive

DoubleTree by Hilton Mesa, Arizona March 3-6, 2024

© 2024 TestConX- Image: iStock-1455326382 siep bueneker

Signal Integrity 1

# Effective back-drilling strategies for 200G+ PAM4 Designs

#### Quaid Joher Furniturewala M. Hameem Ur Rahman R&D Altanova

Mesa, Arizona • March 3-6, 2024

TestConX Workshop

www.testconx.org

March 3-6, 2024

Signal Integrity 1

#### TestConX 2024

#### Contents

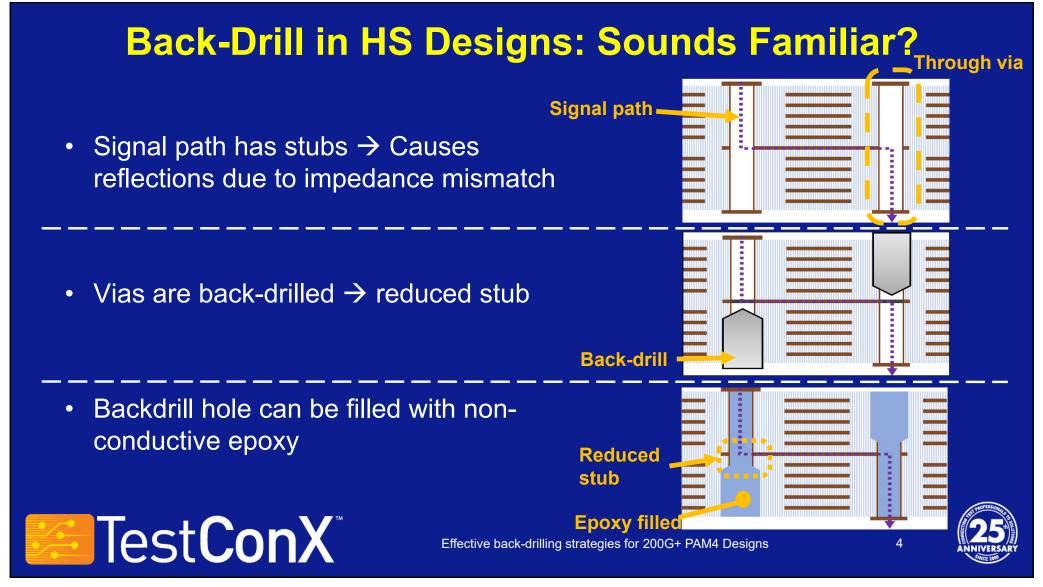

- Need for Back-Drills on Highspeed Designs

- Scope and Objective of the Test

- Test Definition and Measurement Setup

- Simulation Results and Measurement Correlation

- Test Vehicle Validation using Cross section

- Summary and Conclusion

Effective back-drilling strategies for 200G+ PAM4 Designs

www.testconx.org

#### TestConX 2024

Signal Integrity 1

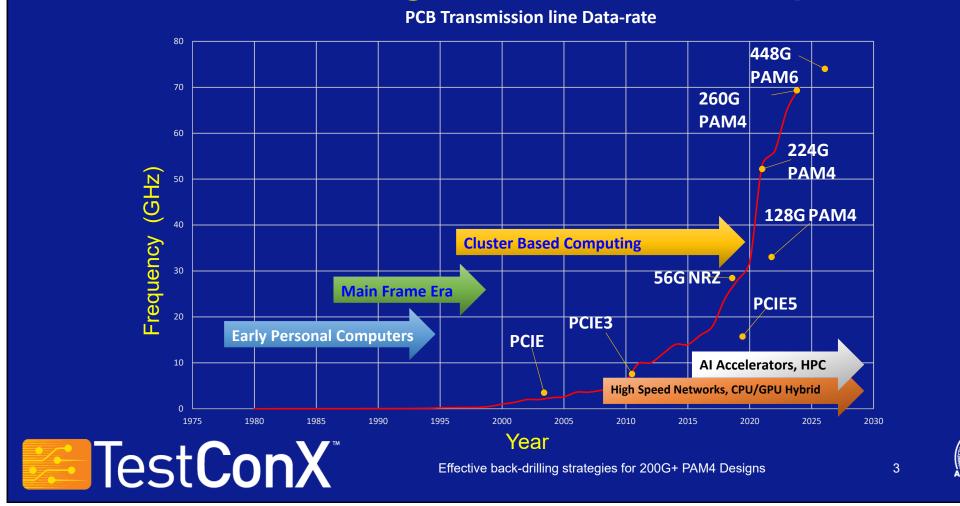

#### The Era of High-Performance Compute

Signal Integrity 1

**Buried via**

#### TestConX 2024

Signal Integrity 1

### **Traditional Via Strategies for HS Lines**

#### **Blind/Buried vias**

- Pros:

- Known minimum stub

- Reduces via density for better power delivery

- Cons:

- longer lead times

- high cost

- Not suitable for high channel count

#### Through-vias with back-drills

- Pros:

- Shorter lead times

- Good cost-effective solution to support signal integrity

- Can be used in conjunction with blind vias

- Cons:

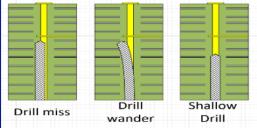

- Stub variation impacts signal integrity

Effective back-drilling strategies for 200G+ PAM4 Designs

Backdrill -

Stub'

Blind via

Known stub

www.testconx.org

5

#### TestConX 2024

Signal Integrity 1

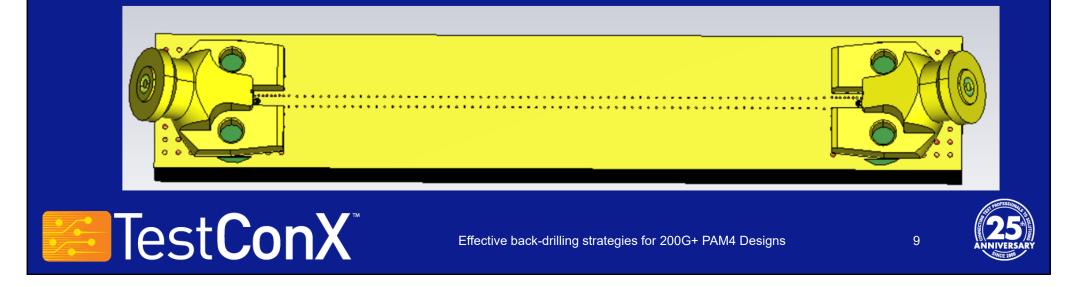

#### **Test Vehicle Design**

#### **Measurement Structures**

50 OHM-2"- STUB 4 MIL - INNER1 TW: 5.6 MIL

- 3 structures per routing layer

- 12 mils stub

- 8 mils stub

- 4 mils stub

- Repeatability: Tested 2x boards

Effective back-drilling strategies for 200G+ PAM4 Designs

www.testconx.org

Signal Integrity 1

#### **Engineering Evaluation for Stub Analysis**

Qs: What stub length is acceptable for my design?

- Test Vehicle Design Considerations:

- Board Material : Meteorwave4000

- Trace Impedance: +/- 5%

- Stack-up:

- Board thickness: 188mils [4.77 mm]

- 32 Layers

- VLP Copper [Ra 4.5 microns]

- Other Consideration:

- Strip-line features: 2" long x 0.0056" wide

- Design constraint: Compression mount connectors, 50 Ohms transmission lines and vias

Test**ConX**

Effective back-drilling strategies for 200G+ PAM4 Designs

www.testconx.org

#### Validation Setup

#### Setup

- Anritsu 70GHz Vector Network Analyzer [VNA]

- Calibrated up to 1.85mm VNA cables

- Connector P/N: 08K80F-40ML5 [1.85mm]

- Test Vehicle Board

TestConX

|    | ••        | ••              | •• |

|----|-----------|-----------------|----|

| •• | ••        | ••              | •• |

|    | ••        | 00              | •• |

|    | ••        | ••              | •• |

| •• | 00        | ••              | •• |

|    | 00        | ••              | •• |

|    | 00        | 00              | •• |

|    | 00        | ••              | •• |

|    | 00        | 00              | •• |

|    | 00        | 00              | •• |

|    | 00        | 00              | 00 |

| •• | 00 301732 | 3001            | •0 |

|    | R8        | $D \mathcal{O}$ |    |

| O  | Alt       | anova.          | Ø  |

Effective back-drilling strategies for 200G+ PAM4 Designs

Session 2

Presentation 2

www.testconx.org

#### TestConX 2024

Signal Integrity 1

#### **Modeling Setup**

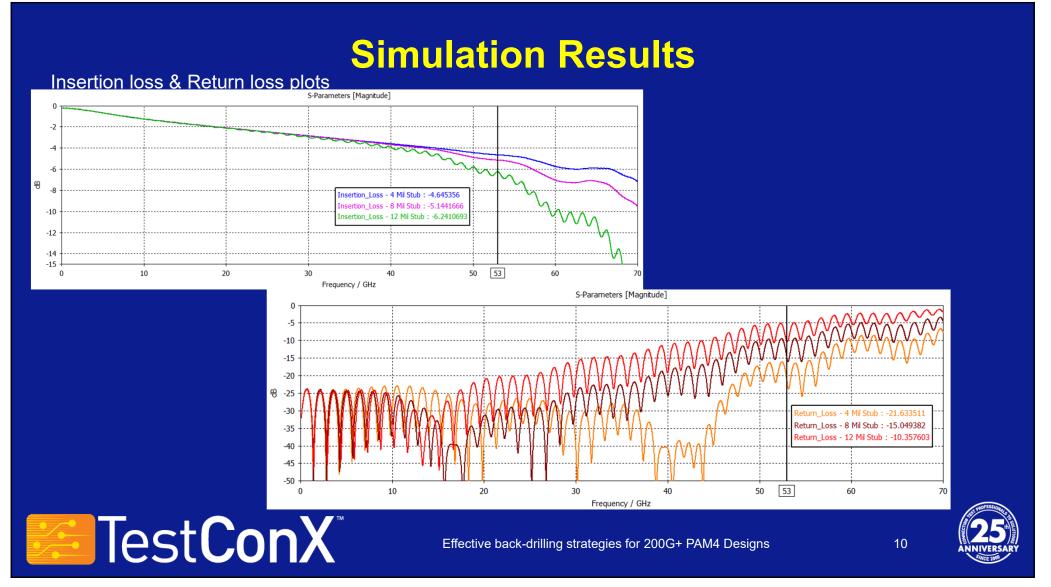

- Modeled with a Full 3D solver [Microwave Studios]

- 4, 8 and 12 mils stub up to 70GHz sweep

- Invisible Vias!

- Copper roughness accounted

#### TestConX 2024

Signal Integrity 1

TestConX Workshop

www.testconx.org

March 3-6, 2024

Signal Integrity 1

#### TestConX 2024

TestConX Workshop

www.testconx.org

March 3-6, 2024

#### TestConX 2024

Signal Integrity 1

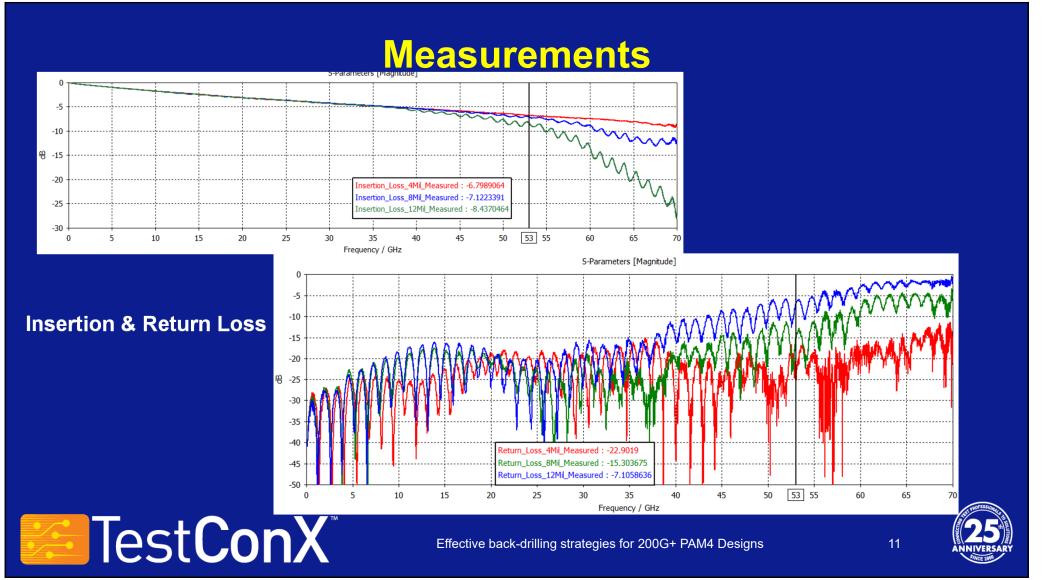

#### **Measurements**

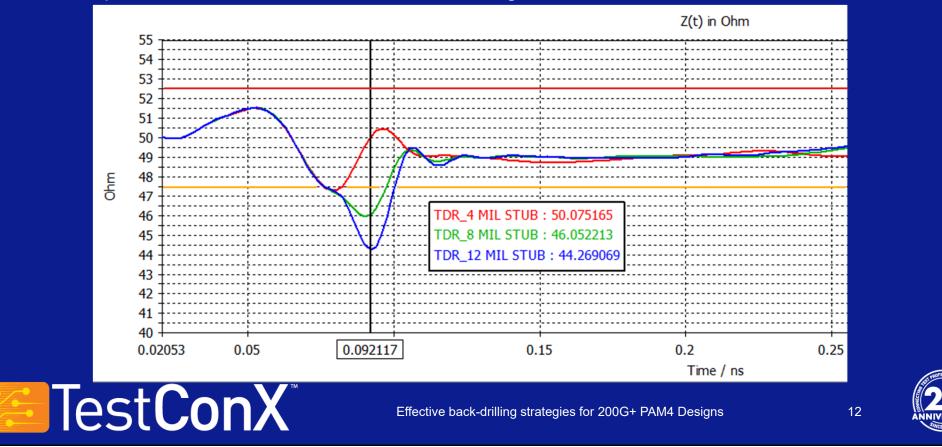

TDR

Clear Impedance variation is observed when looking at the TDR

#### TestConX 2024

Signal Integrity 1

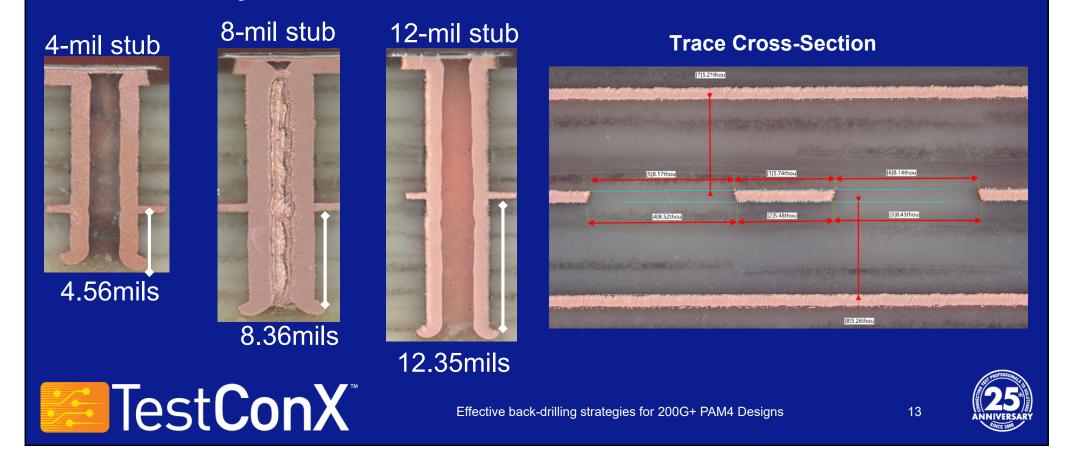

• Boards were cross-sectioned to validate stub length. Measured structures are within manufacturing limits:

Session 2 Presentation 2

Signal Integrity 1

Signal Integrity 1

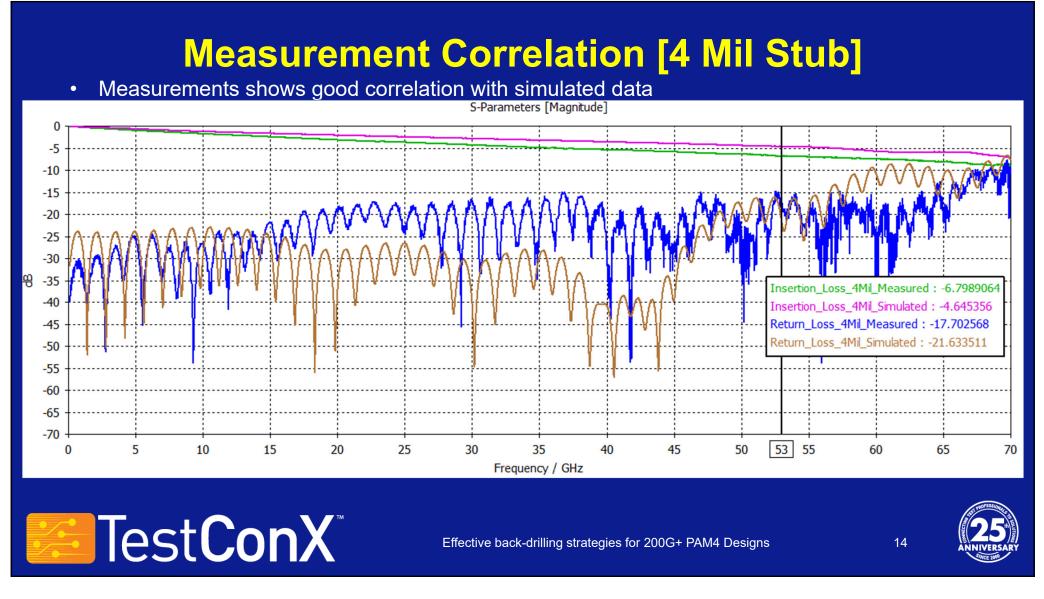

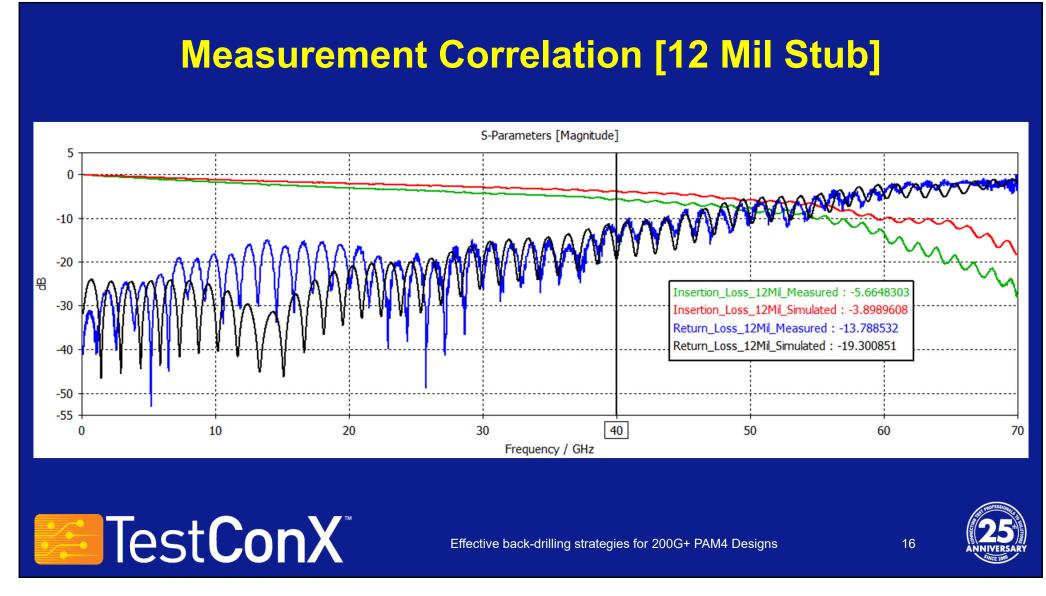

#### **Measurement Correlation [8 Mil Stub]** S-Parameters [Magnitude] -5 -15 -20 -25 -30 Insertion Loss 8Mil Measured : -6.6561244 岛 -35 Insertion\_Loss\_8Mil\_Simulated : -4.8926178 -40Return\_Loss\_8Mil\_Measured : -15.010067 -45 Return\_Loss\_8Mil\_Simulated : -13.192323 -50 -55 -60 -65 -70 50 25 35 55 5 10 15 20 30 40 45 60 65 0 70 Frequency / GHz Test**ConX**® Effective back-drilling strategies for 200G+ PAM4 Designs 15

Session 2 Presentation 2

Signal Integrity 1

Session 2 Presentation 2

Signal Integrity 1

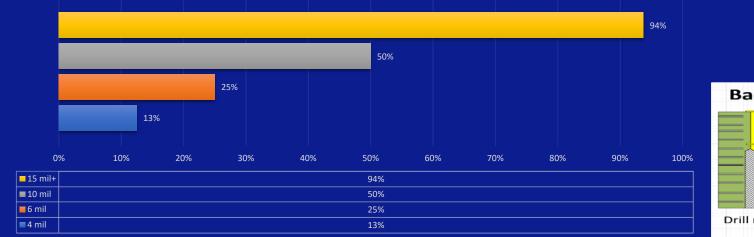

### **Capability Matrix for Advance Back-Drilling**

• Estimated market breakdown for Advance ATE FAB back-drilling capability

**Back-Drill Capability for Advance ATE FAB Shops**

17

🗖 15 mil+ 🔳 10 mil 📕 6 mil 🔳 4 mil

- 4 mil back-drills is critical for 200G+ PAM4 speeds

- Make sure your board vendor has 4 mil back-drill technology

Effective back-drilling strategies for 200G+ PAM4 Designs

Signal Integrity 1

#### **Summary and Results**

- Back-drills; unlike growing perception is still highly effecting technique for stub removal

- With proper back-drill stub control, 70+ GHz performance can be achieved on PCBs

- With manufacturing tolerances accounted, conservatively; 12 mil or better Back-drills can be used for up to 35 GHz design and 8 mils or better up to 50GHz. For 50GHz+\_Design a premium back-drill under 6 mil is advised.

- Make sure to account for PCB manufacturing tolerances when selecting back-drills. Manufacturing tolerance can account for +/-5% to +/-10%

- Other critical parameters as material selection, impedance control, via optimization, etch control, plating features etc. are equally important considerations

| Speed/Modulation                                             | Nyquist | PCB Material             | Stub<br>(Simulations) | PCB Impedance<br>Tolerance [Max] |  |  |

|--------------------------------------------------------------|---------|--------------------------|-----------------------|----------------------------------|--|--|

| 28Gbps NRZ / PAM2                                            | 14GHz   | METWAVE2K                | 12 mil                | +/-10%                           |  |  |

| 56Gbps PAM4                                                  |         | METWAVE2K                | 12 mil                | +/-10%                           |  |  |

| PCIE Gen5                                                    | 16GHz   | METWAVE2K                | 12 mil                | +/-10%                           |  |  |

| 56Gbps NRZ / PAM2                                            | 28GHz   | METWAVE4K                | 10 mil                | +/-5%                            |  |  |

| 112Gb PAM4                                                   |         | METWAVE4K                | 10 mil                | +/-5%                            |  |  |

| 212G PAM4                                                    | 53GHz   | MW4K / MW8K/TACHYON 100G | 6 mil                 | +/-5%                            |  |  |

| 224G PAM4                                                    | 56GHz   | MW4K / MW8K/TACHYON 100G | 6 mil                 | +/-5%                            |  |  |

| 260G PAM4                                                    | 65GHz   | METWAVE8K/TACHYON 100G   | 4 mil                 | +/-5%                            |  |  |

| 280G PAM4                                                    | 70GHz   | METWAVE8K/TACHYON 100G   | 4 mil                 | +/-5%                            |  |  |

| Effective hashed with a starte size for 0000 + DANAA Designs |         |                          |                       |                                  |  |  |

Effective back-drilling strategies for 200G+ PAM4 Designs

Test**ConX**

Signal Integrity 1

#### TestConX 2024

#### **Honorable Mentions**

#### **RDA performance validation team:**

- Henry Lai

- Jacob Neely

#### & RDA Front End Engineering:

- Pravin Alurkar

- Syed Raza Ali Rizvi

- Irfan Khalid

Effective back-drilling strategies for 200G+ PAM4 Designs

25 ANNIVERSA

www.testconx.org

### **COPYRIGHT NOTICE**

The presentation(s) / poster(s) in this publication comprise the Proceedings of the TestConX 2024 workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the TestConX 2024 workshop. This version of the presentation or poster may differ from the version that was distributed at or prior to the TestConX 2024 workshop.

The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors. There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation / poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

"TestConX", the TestConX logo, the TestConX China logo, and the TestConX Korea logo are trademarks of TestConX. All rights reserved.