# **Copyright Notice**

The presentation(s)/poster(s) in this publication comprise the Proceedings of the 2017 BiTS Workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2017 BiTS Workshop. This version of the presentation or poster may differ from the version that was distributed in hardcopy & softcopy form at the 2017 BiTS Workshop. The inclusion of the presentations/posters in this publication does not constitute an endorsement by BiTS Workshop or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by BiTS Workshop. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop. All rights reserved.

Teaming Up - Handler / Test Cell

$S_{ession} 7$

Mike Ramsey Session Chair

**BiTS Workshop 2017 Schedule**

# **Solutions Day**

Wednesday March 8 - 8:00 am

#### **Teaming Up**

"Applying FEA Simulation for Test Interface Unit"

Jason Koh - Test Tooling Solutions Group

"BI RHINO Handling Solution"

Yaniv Raz-Intel Corporation

"Optical Device Testing at Wafer Level and Package Devices"

Carl Kasinski – Aehr

"Fan-in WLCSP Test Requirements"

Mike Frazier - Mike Frazier

# Fan-In WLCSP Test Strategy

Mike Frazier Xcerra Corporation

BiTS Workshop March 5 - 8, 2017

#### **Contents**

- WLCSP Market Overview

- Changes in the Industry (Inflection Point)

- Post Saw Test Process Description

- Evaluation Summary

- Conclusion

Teaming Up - Handler / Test Cell

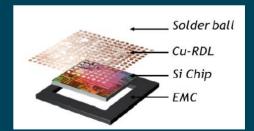

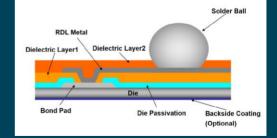

#### **Fan Out WLCSP**

#### Definition

- Fan out implies that the ball grid array is larger than the die

- Die is encapsulated in molding with RDL layer covering die AND molding

- Package sizes up to 25mm X 25 mm today

- Multi-chip and/or passive integration possible

- Lower cost and smaller package compared to FCBGA

- Larger area for contact balls

#### Disadvantages

- Higher cost and larger die than FI-WLCSP

- Yield (associated with placement accuracy)

Fan-In WLCSP Test Strategy

Teaming Up - Handler / Test Cell

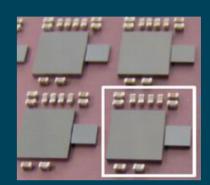

#### Fan-In WLCSP

#### Definition

- Fan in implies that the contact balls fit within the die size

- Bare die or encapsulated up to 7mm X 7mm

#### Advantages

- Smallest possible package size (X,Y and Z dimensions)

- Lowest possible packaging cost (No Substrate RDL)

- High performance (no bond wires, short signal length, low cap.)

#### Disadvantages

- Limited pin count (space for contact balls)

- Reliability (chipping, cracks, shipping....)

- Single die, no support for passives

Fan In WLCSP devices make up 30% of packages in cell phone today

Fan-In WLCSP Test Strategy

Teaming Up - Handler / Test Cell

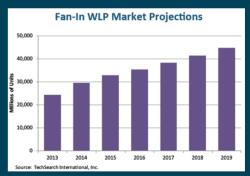

# **Fan In Market Summary**

Fan in WLCSP market is significantly larger than FO-

**WLCSP**

RF Transceivers

- PMIC

Baseband

- RF Power amps

Touch controllers

- MEM's

- End applications

- Cell Phones

- Automotive

Tablets

- Wearables

- IOT

- more

- Fine Pitch

- 0.4 mm ball pitch is typical

- 0.3mm is leading edge for "direct to board"

- 0.2mm is leading edge for substrate placement

CAGR ~9%

**Fan-In WLCSP Test Strategy**

# **Quality Demand of the Industry**

- Automotive has been traditionally the driver for low defect requirements

- Consumer devices had less stringent quality standards...but this has changed

Drive to near zero defect parts per million (PPM) → defect parts per billion (PPB)

Fan-In WLCSP Test Strategy

### **Traditional Process Flow**

#### Challenges:

- Test at start of backend processing

- Device picking and Saw process after test

Fan-In WLCSP Test Strategy

Source: Microfab

Teaming Up - Handler / Test Cell

## **Post Saw Test Advantages**

### True Final Test of singulated WLCSP devices

- Improved Quality

- Test Process moved to end of back end processing (PST)

- RMA / device retest

- Same retest capability as production test

Fan-In WLCSP Test Strategy

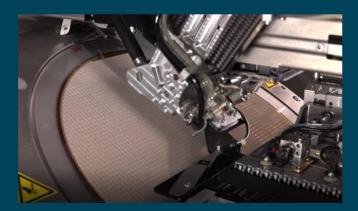

# Post Saw Test Process Steps (Device Pick)

- Input from sawn Film frame or Tape and Reel

- Device Placement onto test "substrate"

- InCarrier, glass wafer, vacuum chuck....

Fan-In WLCSP Test Strategy

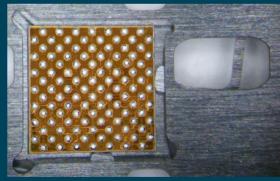

#### InCarrier Features and benefits

- Easy handling of hundreds of singulated WLCSP devices in a strip format

- Mechanical alignment for highest accuracy

- Device retention exceed "drop test"

- Supports Lots on hold

- Improved throughput with 100% touch efficiency

- Supports Full Tri-temp test environment

- Handling WLCSP for Engineering

- Device handling for characterization

- Burn-in / Environmental

Up to 300 devices / InCarrier

Fan-In WLCSP Test Strategy

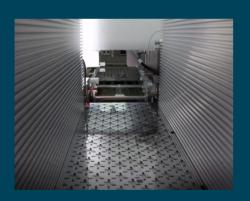

# Post Saw Test Process Steps (Device Test)

- Present singulated devices to ATE test

- Strip Handlers, Probers

- Test is the most expensive process step in back end processing

- Desire is to have highest possible utilization

InStrip with MEM's stimulus

Fan-In WLCSP Test Strategy

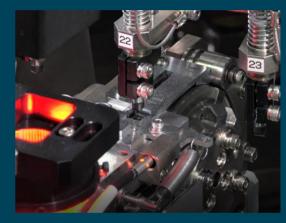

# Post Saw Test Process Steps (Tape and Reel)

- Remove tested singulated devices for test "substrate" for placement into T+R

- Device Rotation

- Laser Mark

- Mark Inspection

- Sidewall Inspection

- Ball side Inspection

- Tape and reel

- Pre and post seal inspection

Fan-In WLCSP Test Strategy

# **Summary of Results**

- System Validation on OSAT floor

- ESD, safety, operational validation passed

- Correlation achieved to existing probe results

- Large sample run of parts from T+R

- Reject level detected at 500PPM during first pass

- Looped sample of units 4 times with 0 rejects detected

- Demonstrated 14% higher test cell throughput

Fan-In WLCSP Test Strategy

### Conclusion

- Quality demand is changing the way people will test WLCSP devices.

- New process flow eliminates test escapes created by singulation process

- Enables true Final Test of WLCSP devices

- Proven Gentle and reliable handling of singulated WLCSP packages

- Improved test cell efficiency

- Flexibility for wide range of applications

Fan-In WLCSP Test Strategy