# **ARCHIVE 2010**

#### TECHNIQUES, COMPONENTS & ADVANCES FOR NEXT GENERATION TEST

Next Generation CiS (Capacitor in Socket) Featuring Discrete Capacitors and Elastomer Hybrid Schemes

Shaul Lupo, Omer Vikinski—Intel Corporation David Bogardus, Khaled Elmadbouly, Cody Jacob—Interconnect Devices Inc.

#### **Multi Level Stacked Socket - Challenges & Solutions**

Mike Fedde, Ranjit Patil, Ila Pal, Vinayak Panavala—Ironwood Electronics

#### Advances in WSP - Wafer Socket Pogo-Pin Probing

Norman Armendariz, James Tong—Texas Instruments

#### Answering the Call

Thomas N. Bresnan—R&D Circuits

#### **COPYRIGHT NOTICE**

The papers in this publication comprise the proceedings of the 2010 BiTS Workshop. They reflect the authors' opinions and are reproduced as presented , without change. Their inclusion in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, BiTS Workshop LLC, or the authors.

There is NO copyright protection claimed by this publication or the authors. However, each presentation is the work of the authors and their respective companies: as such, it is strongly suggested that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

All photographs in this archive are copyrighted by BiTS Workshop LLC. The BiTS logo and 'Burn-in & Test Socket Workshop' are trademarks of BiTS Workshop LLC.

Techniques, Components & Advances for Next Generation Test

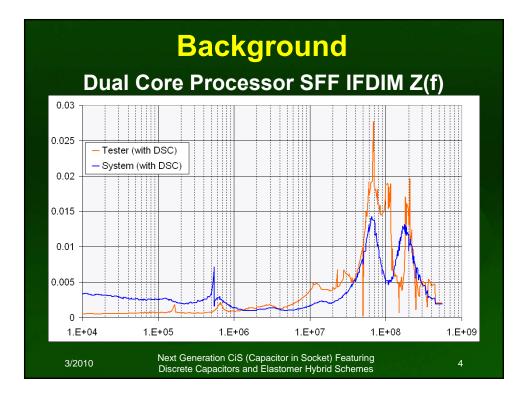

## Next Generation CiS (Capacitor in Socket) Featuring Discrete Capacitors and Elastomer Hybrid Schemes

Shaul Lupo, Omer Vikinski Intel

David Bogardus, Khaled Elmadbouly, Cody Jacob Interconnect Devices, Inc.

2010 BiTS Workshop March 7 - 10, 2010

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

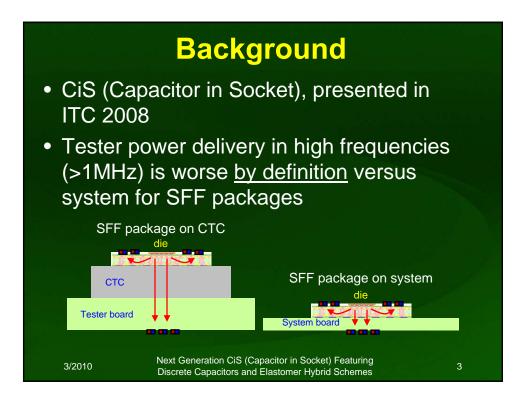

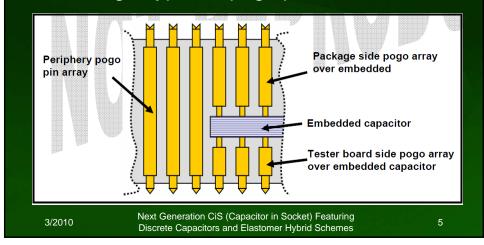

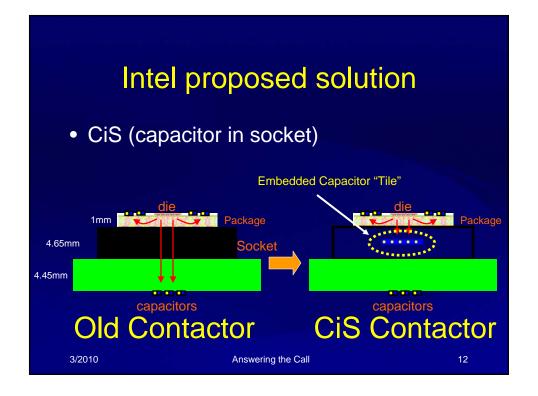

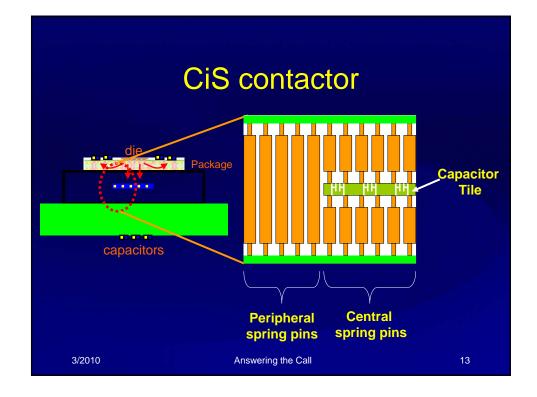

#### **CiS Solution Approach**

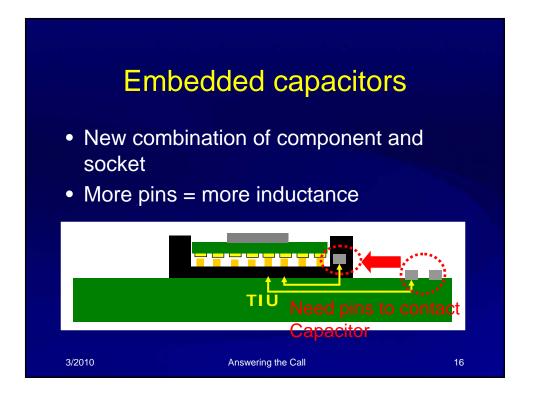

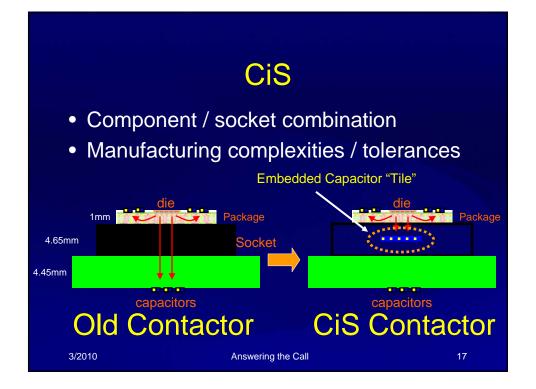

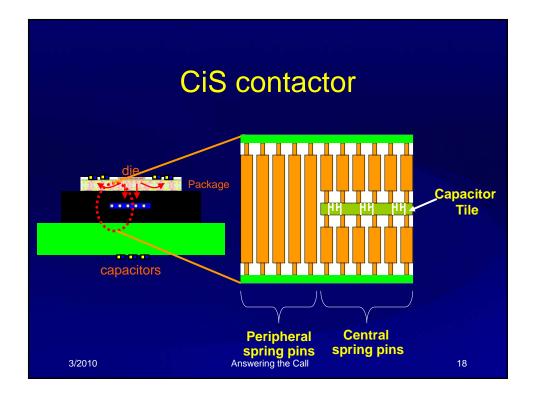

- Embedded array capacitor in the test-socket used to reverse this equation.

- Including 3 types of pogo pins.

# <section-header><section-header><text><image><image><image><image><image>

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

# <section-header><section-header><text><text><text><text>

Techniques, Components & Advances for Next Generation Test

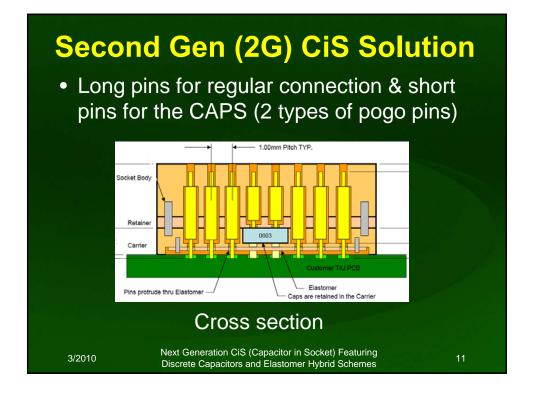

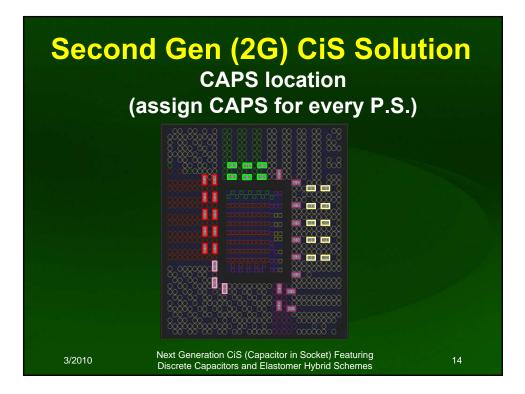

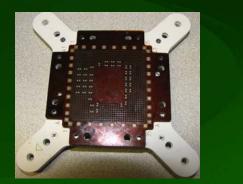

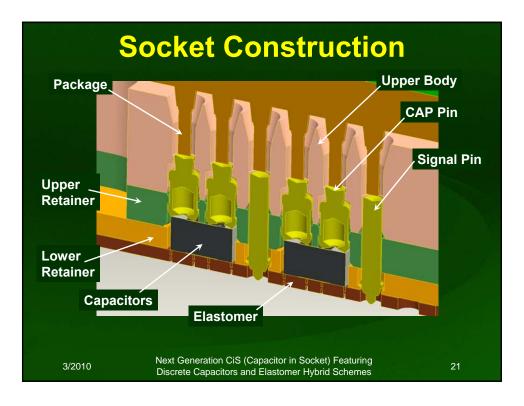

## Second Gen (2G) CiS Solution

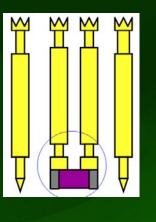

- Modify pogo pin tip to a wider one to enable good contact to CAP pad, meet CAP case. Standard LGA plunger tip may miss the cap electrodes due to tolerance variations.

- The custom pin design to penetrate oxidization layer on capacitor surfaces to insure low contact resistance.

3/2010

Next Generation CiS (Capacitor in Socket) Featuring Discrete Capacitors and Elastomer Hybrid Schemes

Techniques, Components & Advances for Next Generation Test

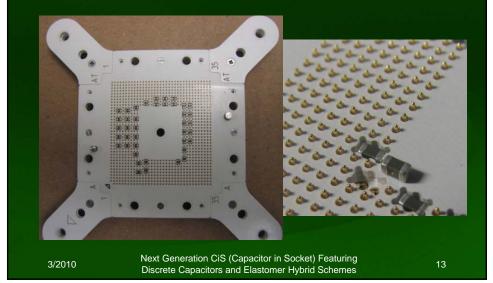

# Second Gen (2G) CiS Solution

• Bottom side: Assign cavities for 0603 CAPS

Techniques, Components & Advances for Next Generation Test

# Second Gen (2G) CiS Solution

• Assemble Elastomer (Kapton material), on bottom side

• Elastomer is functioning as a retainer

for non CAP pogo pins and as continuity BTW CAP to PCB in CAPS edge location

Next Generation CiS (Capacitor in Socket) Featuring Discrete Capacitors and Elastomer Hybrid Schemes

15

#### dCiS + Elastomer Socket 2G Advantages over 1G CiS Solution

• Lower Cost:

3/2010

- Due to using two types of pogo pins VS. 3 types in previous solution.

- Due to using longer pins in CAPS corridor since CAPS located at the bottom. At the previous solution array cap located in the middle, thus pogo pins are shorter.

3/2010

Next Generation CiS (Capacitor in Socket) Featuring Discrete Capacitors and Elastomer Hybrid Schemes

Techniques, Components & Advances for Next Generation Test

- <u>Cycling:</u> Life cycle is higher in the new solution since pogo pins at CAPS corridor are longer

- <u>Flexibility</u>: CAPS replacement to another values and CAPS depopulation. Previous solution is not flexible, need new array CAP (with new CAPS values) for replacement, no option to do CAPS depopulation.

3/2010

Next Generation CiS (Capacitor in Socket) Featuring Discrete Capacitors and Elastomer Hybrid Schemes

17

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

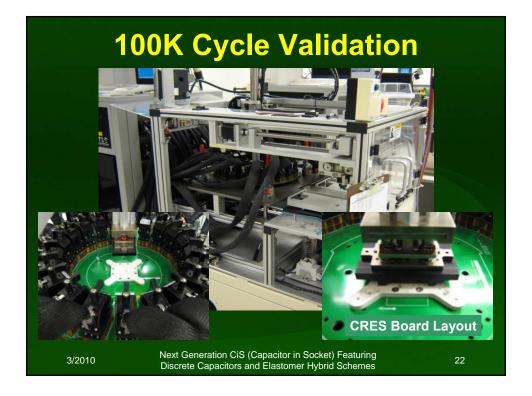

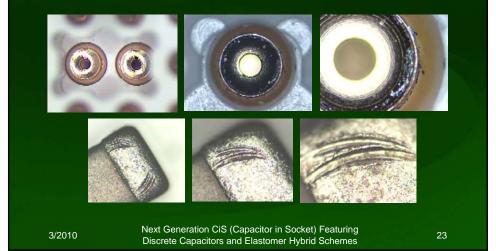

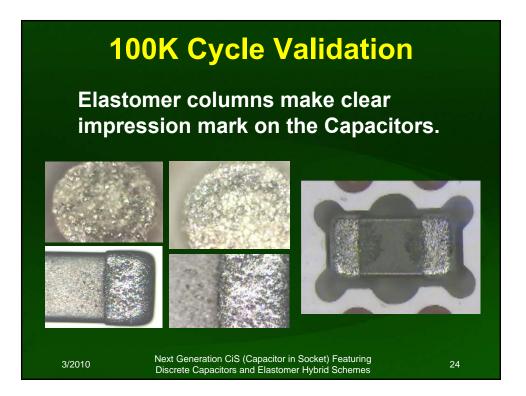

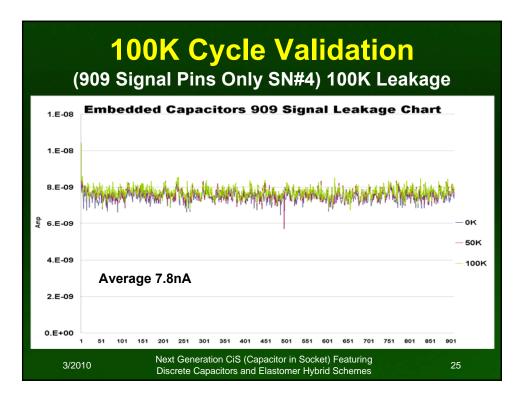

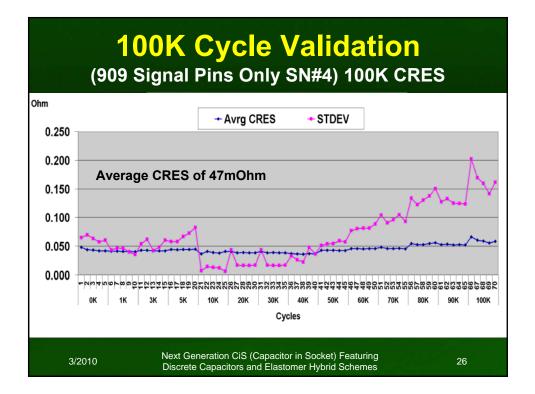

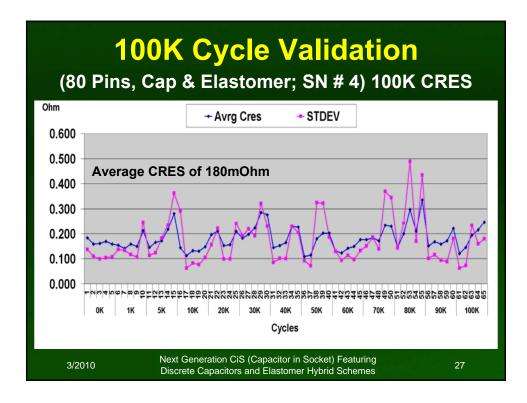

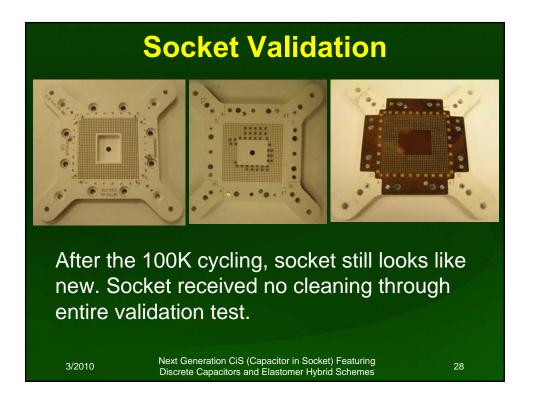

#### **100K Cycle Validation**

The bottom of the Spring Probe Ring is making strong mark on the Capacitors.

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

| Content                                                  |   |

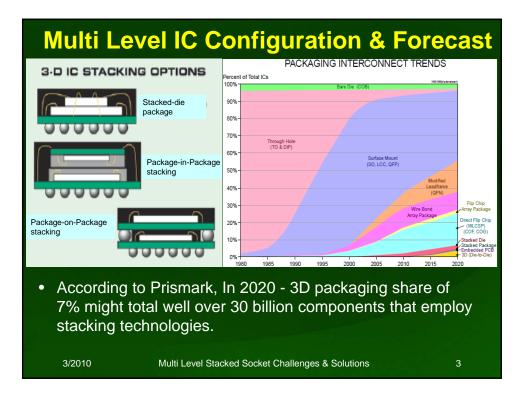

|----------------------------------------------------------|---|

| Introduction                                             |   |

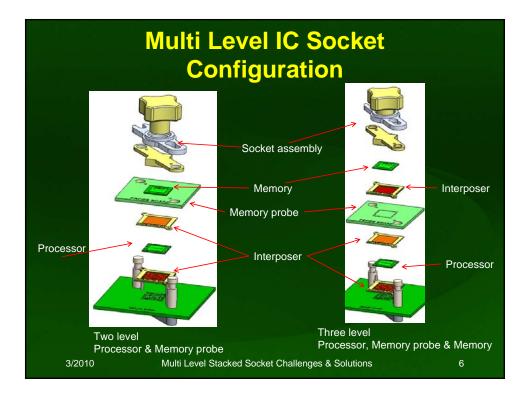

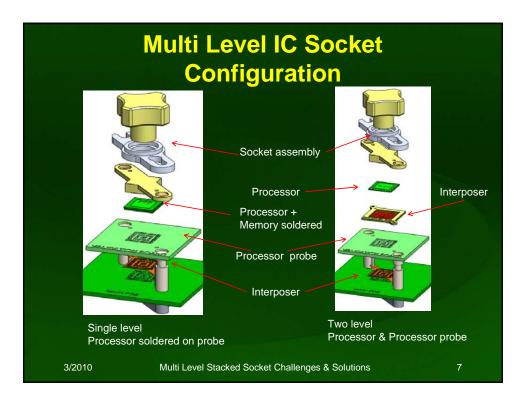

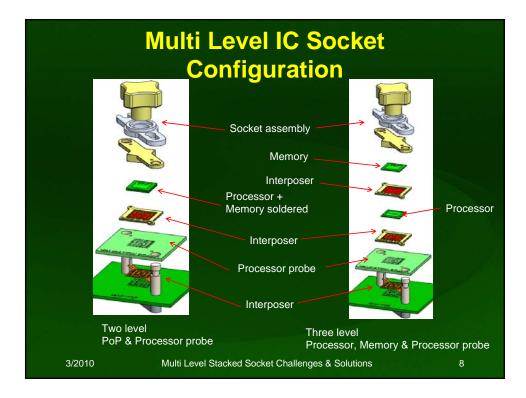

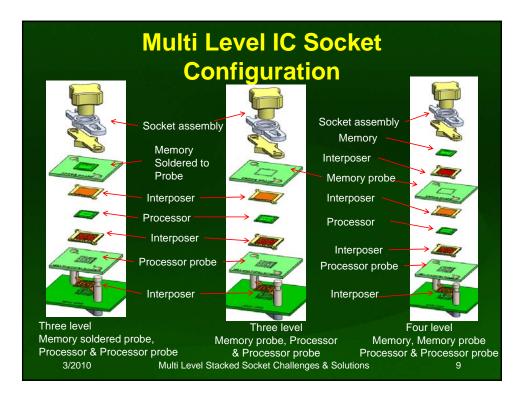

| <ul> <li>Multi Level IC Configuration</li> </ul>         |   |

| <ul> <li>Multi Level IC Test Need</li> </ul>             |   |

| <ul> <li>Multi Level IC Socket Configuration</li> </ul>  |   |

| <ul> <li>Electrical Simulation</li> </ul>                |   |

| <ul> <li>Stack up Alignment Challenges</li> </ul>        |   |

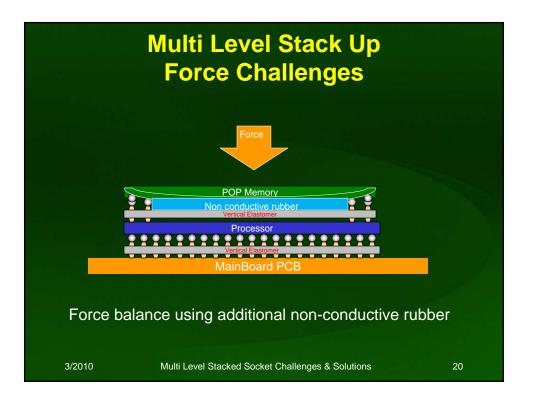

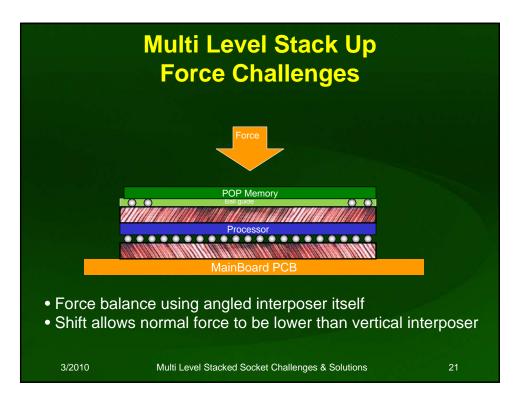

| <ul> <li>Stack up Force Challenges</li> </ul>            |   |

| Conclusion                                               |   |

|                                                          |   |

| 3/2010 Multi Level Stacked Socket Challenges & Solutions | 2 |

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

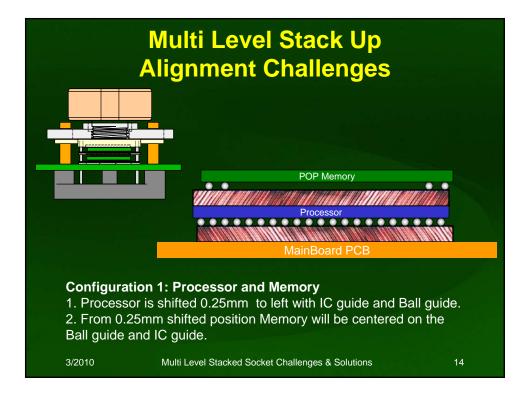

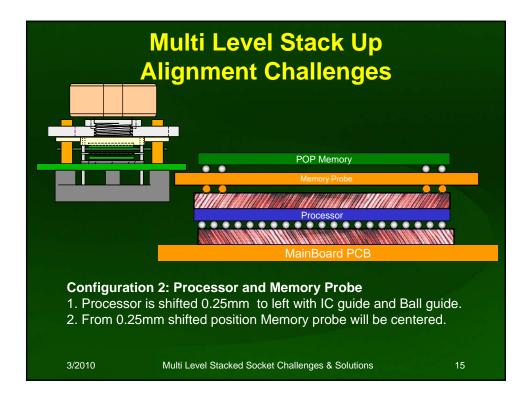

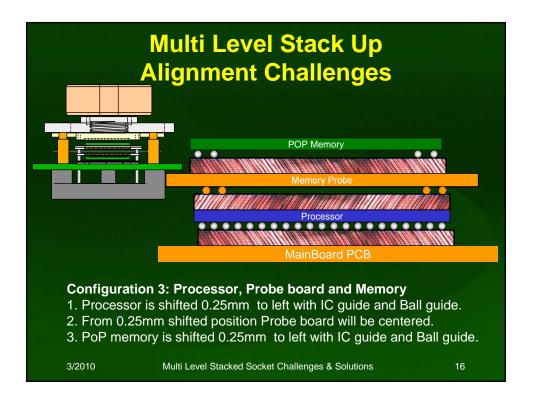

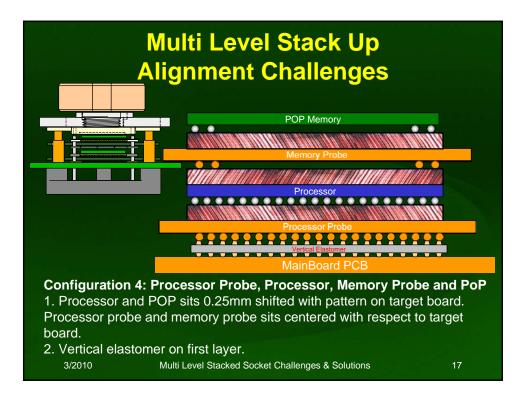

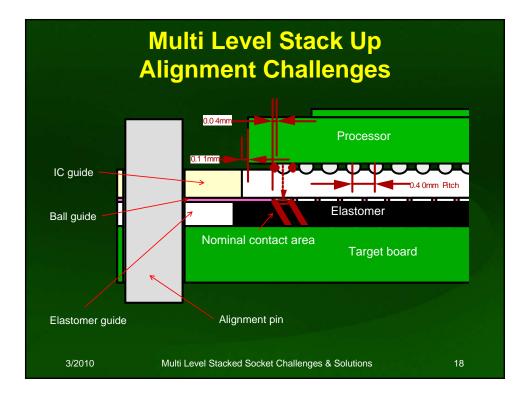

| Multi Level Stack Up<br>Alignment ChallengesProcessor/Elastomer/PCB tolerance±PCB Alignment Hole position± +0.025mmBall guide Alignment Hole position± +0.025mmPCB Pad location/Size± +0.05mm=0.1mm off from nominal locationWith 0.24mm minimum pad diameter for 0.4mm pitch BGA,<br>elastomer contacts more then 58% of the pad. This XY<br>variation occurs on each level of the stack up. Similar<br>calculations were made for Z variations and manufacturing<br>tolerances were updated such that 60% of pad is covered by |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

Techniques, Components & Advances for Next Generation Test

#### **Multi Level Stack Up Force Challenges** Force data for a four level interconnect stack up shown as per ball count Series network of forces are balanced at each level either by using an additional non-conductive rubber or elastomer by itself Elastomer Ball Count Force/Ball, gm Total Force, Kg PoP Angle 5.07 169 30 Memory Probe Memory Probe 169 30 5.07 Angle Processor Processor Angle 515 30 15.45 Processor Probe Processor Probe Straight 515 18.025 35 Target Board 3/2010 Multi Level Stacked Socket Challenges & Solutions 22

Techniques, Components & Advances for Next Generation Test

#### Conclusion

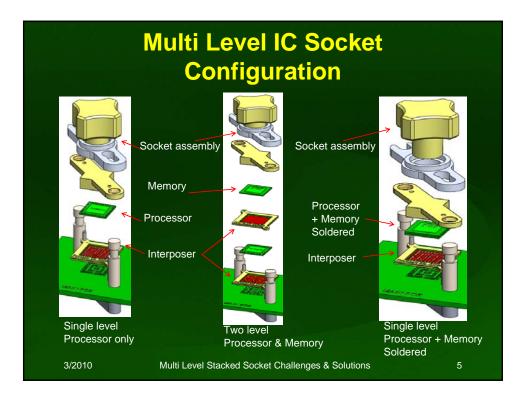

- 3D packages are the future

- Pitch, pin count, performance complexities increase due to consumer demand

- Two level package needs four level interconnect for development

- XYZ alignment challenges in each interconnect level push manufacturing capabilities to its extreme

- Force balancing at each level enables innovative design and requires new materials with unique properties

3/2010

Multi Level Stacked Socket Challenges & Solutions

23

Techniques, Components & Advances for Next Generation Test

# Advances in WSP- Wafer Socket Pogo-Pin Probing

Norman Armendariz James Tong

2010 BiTS Workshop March 7 - 10, 2010

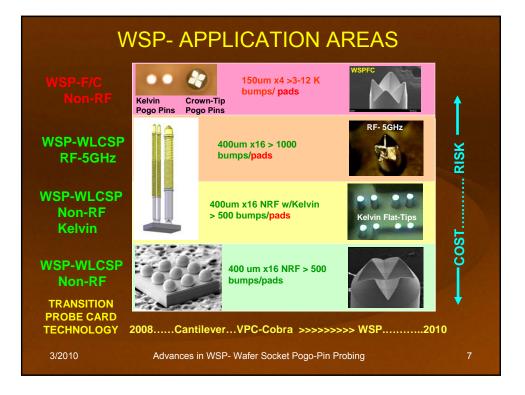

|        | CONTENT                                        |   |

|--------|------------------------------------------------|---|

|        | Introduction                                   |   |

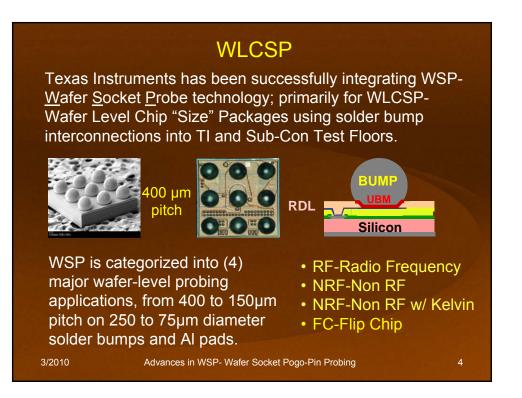

| •      | WLCSP- Wafer Level Chip Size Packaging         |   |

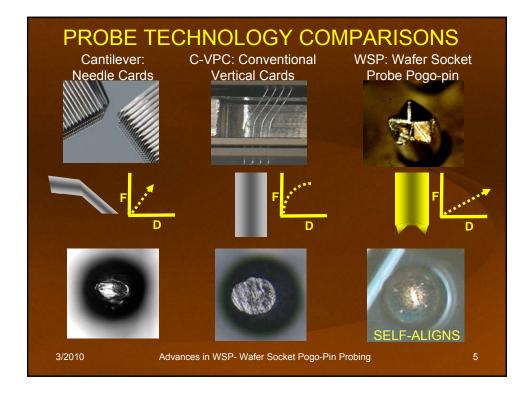

| •      | Probe Technology Comparisons                   |   |

| •      | WSP Advantages                                 |   |

| •      | Application Areas                              |   |

| •      | WSP vs. Cantilever on Bumps                    |   |

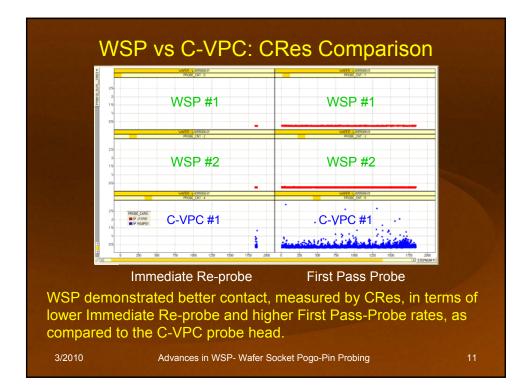

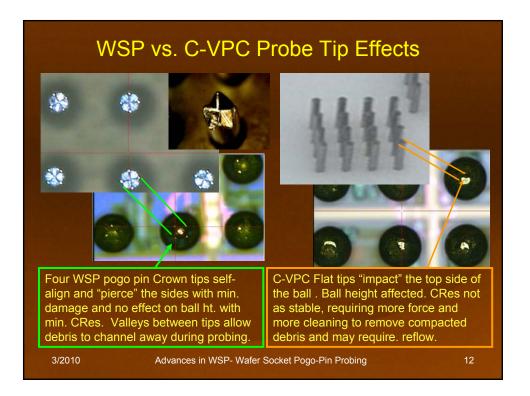

| •      | WSP vs. C-VPC on Bumps                         |   |

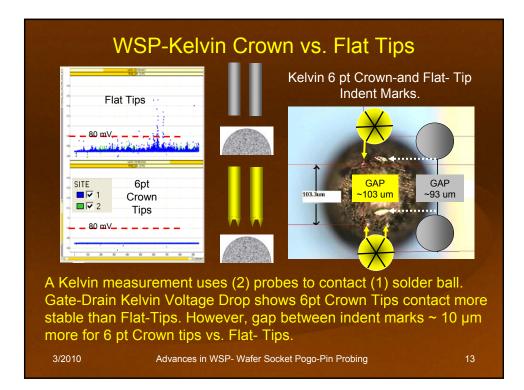

|        | WSP Kelvin Crown vs. Flat-Tips                 |   |

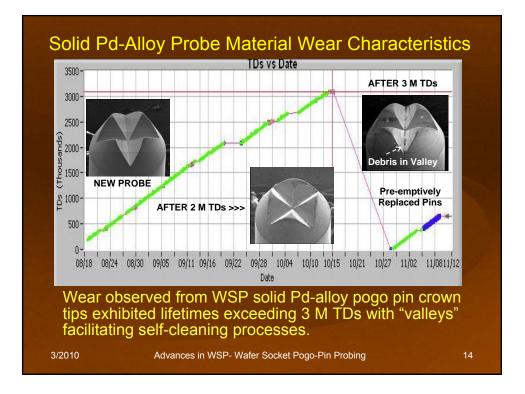

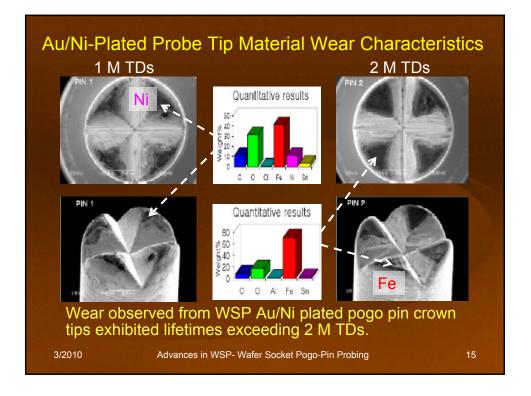

| •      | Effect of Probe Materials on Lifetime          |   |

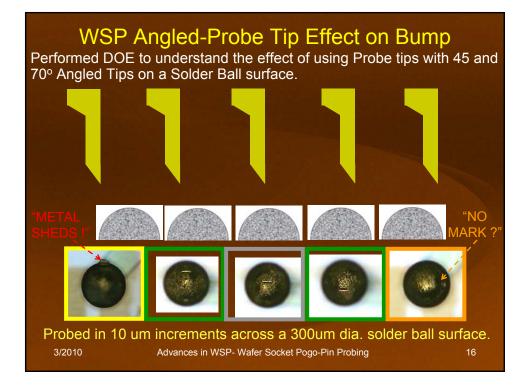

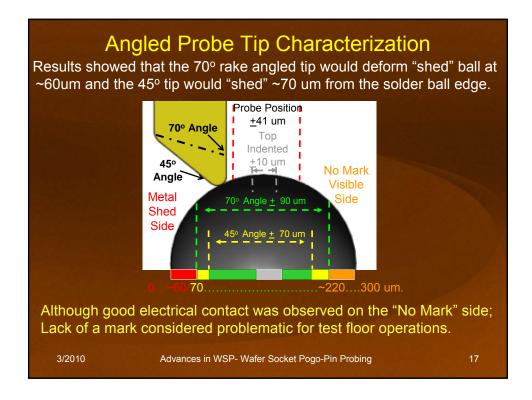

| •      | Effect of Angled Probe Tips on Bumps           |   |

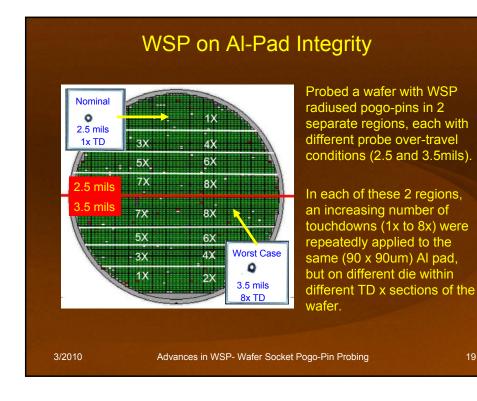

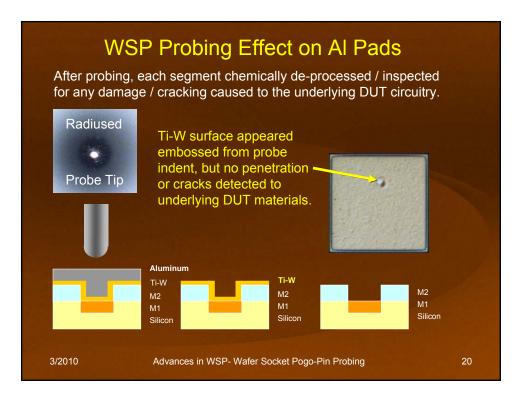

|        | Effect on Bump and Al-Pads Integrity           |   |

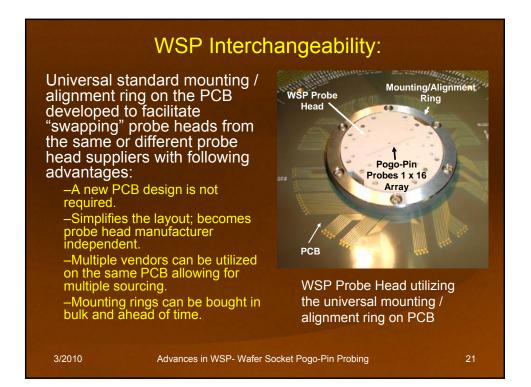

| •      | WSP Interchangeability                         |   |

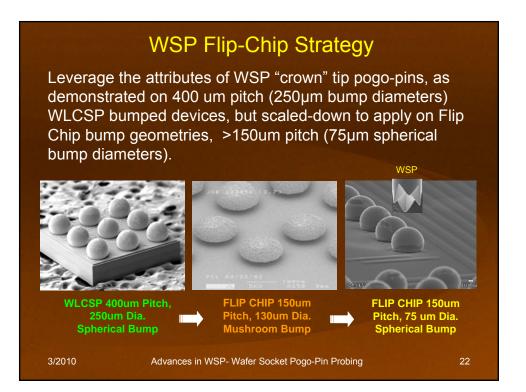

| •      | WSP Flip Chip Strategy                         |   |

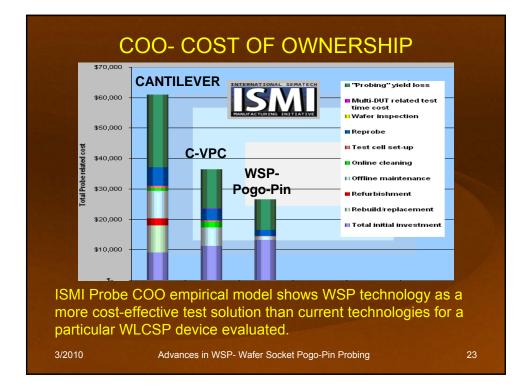

|        | WSP COO                                        |   |

|        | WSP Summary                                    |   |

| 3/2010 | Advances in WSP- Wafer Socket Pogo-Pin Probing | 2 |

Techniques, Components & Advances for Next Generation Test

#### INTRODUCTION

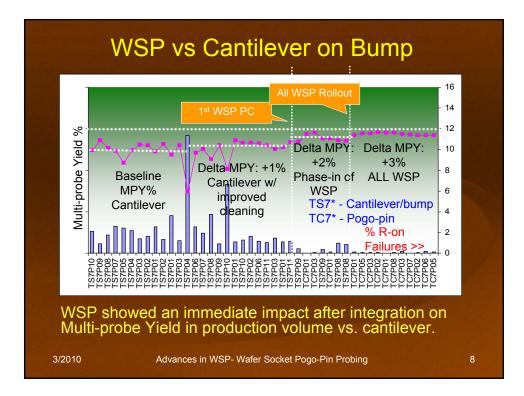

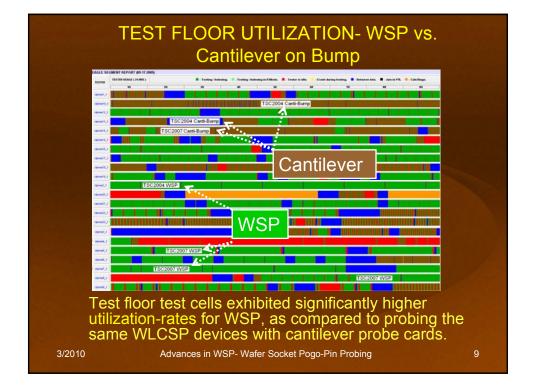

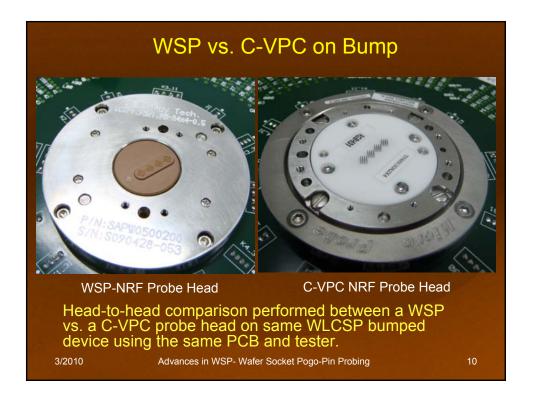

- WSP- <u>Wafer Socket Probe card technology based on pogo-pin contacts has been qualified for testing WLCSP-Wafer-Level Chip Size Packages on 250 µm diameter solder bumps at 400 µm pitch, instead of current Cantilever and C-VPC; Conventional Vertical Probe Cards.

</u>

- WSP card technology has demonstrated a reduced cost of operations with increased electrical and physical performance, and is increasingly displacing conventional wafer-probe methods for WLCSP Devices requiring RF, Non-RF and Non-RF w/ Kelvin capabilities on test floors.

3/2010

Advances in WSP- Wafer Socket Pogo-Pin Probing

3

Techniques, Components & Advances for Next Generation Test

| WSP MAJOR ATTRIBUTES                                                      |                                                                        |  |  |  |  |  |

|---------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|--|

| <ul> <li>Self-Aligning 4 pts</li> <li>Bump Damage &lt; CVPC</li> </ul>    | •CRes < CVPC<br>•Cost ~85% of CVPC                                     |  |  |  |  |  |

| No Reflow Required                                                        | • Cleaning < CVPC                                                      |  |  |  |  |  |

| <ul> <li>Hand-Test Capable</li> <li>Lifetime &gt; 3 M TDs</li> </ul>      | <ul> <li>Kelvin Capable 400um</li> <li>Deflection &gt; CVPC</li> </ul> |  |  |  |  |  |

| <ul> <li>PC Analyzer Not Req'd.</li> <li>Single-pin repairable</li> </ul> | <ul> <li>Force &lt; CVPC</li> <li>Interchangeable</li> </ul>           |  |  |  |  |  |

| • Single-pin repairable                                                   | Interchangeable                                                        |  |  |  |  |  |

| 3/2010 Advances in WSP- Wafer Socket Pogo-Pin Probing                     |                                                                        |  |  |  |  |  |

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

| WSP Effect on Bump Integrity                                                                                                                                                                    |       |            |       |                |        |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|-------|----------------|--------|--|--|--|

| CRes Avg<br>(Ω) >                                                                                                                                                                               | Mean  | Std<br>Dev | Min   | Max            |        |  |  |  |

| 0 TDs                                                                                                                                                                                           | 13.65 | 0.4245     | 12.60 | 15.09          |        |  |  |  |

| 30 TDs                                                                                                                                                                                          | 13.85 | 0.4679     | 12.68 | 15.19          |        |  |  |  |

|                                                                                                                                                                                                 | 13.52 | 0.3243     | 12.57 | 14.39<br>15.02 |        |  |  |  |

|                                                                                                                                                                                                 | 13.95 | 0.4577     | 12.52 | 15.02          |        |  |  |  |

| 90 TDs                                                                                                                                                                                          | 14.11 | 0.5381     | 12.61 | 15.50          |        |  |  |  |

| 110 TDs                                                                                                                                                                                         | 14.07 | 0.5734     | 12.60 | 15.24          |        |  |  |  |

| 0-TDs                                                                                                                                                                                           |       | 30         | TDs   |                | 90 TDs |  |  |  |

| No statistically difference observed after repeatedly probing a WLCSP<br>solder ball > 110 TDs, in terms of CRes or damage to RDL or DUT.3/2010Advances in WSP- Wafer Socket Pogo-Pin Probing18 |       |            |       |                |        |  |  |  |

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

| ACKNOWLEDGEMENTS           |                                 |  |

|----------------------------|---------------------------------|--|

| John Hite                  | Alan Castillo                   |  |

| Rich Lewis                 | Rodolfo Gamboa                  |  |

| David Tanner               | Michael Harris                  |  |

| Stan Ferrell               | Dale Ohmart                     |  |

| Scott Delmont              | Minette Ohmart                  |  |

| Charles Hart               | Al Weglietner                   |  |

| Dan Stillman               | Angel Melquiadez                |  |

| Golden King                | Ace Arricivita                  |  |

| Donny Stanton              | Ronald Payumo                   |  |

| Spencer Tang               | Mike Yadzani                    |  |

| Damien Lewis               | Jesse Ko                        |  |

| ECI NHK<br>Uokowo          | WinWay Ardentec                 |  |

| 3/2010 Advances in WSP- Wa | afer Socket Pogo-Pin Probing 25 |  |

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

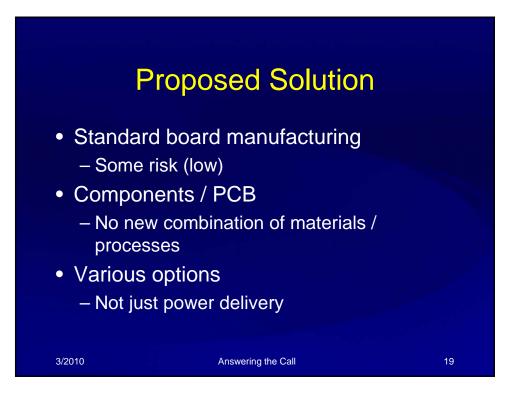

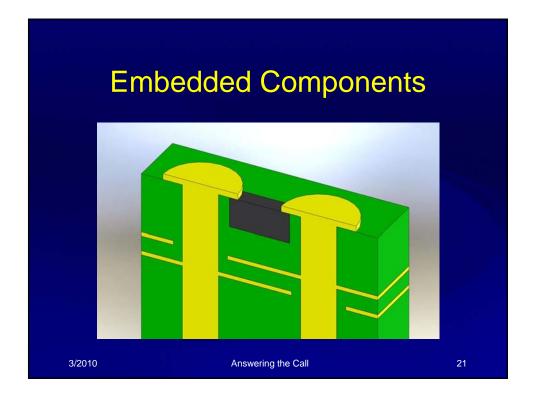

| Proposed Solution                                                                                                                                                                                                                                  |    |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| <ul> <li>Via transition elimination</li> <li>Capacitors assembled on circuit layers <ul> <li>Eliminates need for via to surface and back</li> </ul> </li> <li>Space for vias already allotted <ul> <li>Similar design rules</li> </ul> </li> </ul> |    |  |

| 3/2010 Answering the Call                                                                                                                                                                                                                          | 25 |  |

Techniques, Components & Advances for Next Generation Test

3/2010

## **Session 5**

29

Techniques, Components & Advances for Next Generation Test

Answering the Call

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

**Session 5**

**Session 5**

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test

Techniques, Components & Advances for Next Generation Test